# WT32L064/032 Flash Memory Type 32-bit Microcontroller

**Data Sheet**

Rev. 1.02

February 2022

#### **Copyright Notice**

This data sheet is copyrighted by Weltrend Semiconductor, Inc. Do not reproduce, transform to any other format, or send/transmit any part of this documentation without the express written permission of Weltrend Semiconductor, Inc.

#### **Disclaimers**

#### Right to make change -

This document provides technical information for user. Weltrend Semiconductor, Inc. reserves the right to make change without further notice to any products herein.

#### **Table of Contents**

| Tab  | Table of Contentsi |                                                   |     |  |  |

|------|--------------------|---------------------------------------------------|-----|--|--|

| List | of Fig             | jures                                             | vii |  |  |

| List | of Ta              | bles                                              | ix  |  |  |

| 1    | Gene               | ral Description                                   | 1   |  |  |

| •    | 1.1                | Main Features                                     |     |  |  |

|      | 1.2                | System Block Diagram                              |     |  |  |

|      | 1.3                | System Power Architecture                         |     |  |  |

|      | 1.4                | System Clock Tree                                 |     |  |  |

|      | 1.5                | ARM <sup>®</sup> Cortex™-M0 Processor             |     |  |  |

|      |                    | 1.5.1 Cortex M0 Processor Features                |     |  |  |

|      |                    | 1.5.2 Nested Vectored Interrupt Controller (NVIC) |     |  |  |

|      |                    | 1.5.3 System Timer (SysTick)                      |     |  |  |

| 2    | Pin Δ              | ssignment                                         | 11  |  |  |

| _    | 2.1                | Package                                           |     |  |  |

|      | 2.1                | 2.1.1 LQFP-64                                     |     |  |  |

|      |                    | 2.1.2 LQFP-48                                     |     |  |  |

|      |                    | 2.1.3 QFN-32                                      |     |  |  |

|      | 2.2                | Pin Description                                   | _   |  |  |

|      | 2.3                | Alternate Function I/O Priority                   |     |  |  |

| _    | N/                 | ·                                                 |     |  |  |

| 3    |                    | ory Mapping                                       |     |  |  |

|      | 3.1<br>3.2         | AMBA Bus Address Mapping  APB Memory Space        |     |  |  |

|      |                    | <i>,</i> .                                        |     |  |  |

| 4    |                    | and Clock Control                                 |     |  |  |

|      | 4.1                | Main Features                                     |     |  |  |

|      | 4.2                | Block Diagram                                     |     |  |  |

|      | 4.3                | Register Definition                               |     |  |  |

|      | 4.4                | Functional Description                            |     |  |  |

|      |                    | 4.4.1 Reset                                       |     |  |  |

|      |                    | 4.4.1.1 System Reset                              |     |  |  |

|      |                    | 4.4.1.2 Power Reset                               |     |  |  |

|      |                    | 4.4.1.3 Standby Exit Reset                        |     |  |  |

|      |                    | 4.4.2.1 PLL Clock                                 |     |  |  |

|      |                    |                                                   |     |  |  |

| 5    |                    | r Manage Unit                                     |     |  |  |

|      | 5.1                | Power Management Unit Features                    |     |  |  |

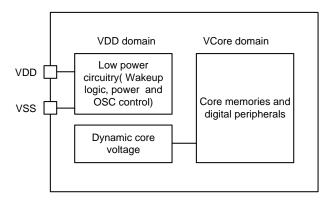

|      | 5.2                | Power Domain Overview                             |     |  |  |

|      | 5.3                | Voltage Regulator                                 |     |  |  |

|      | 5.4                | Dynamic Core Voltage                              |     |  |  |

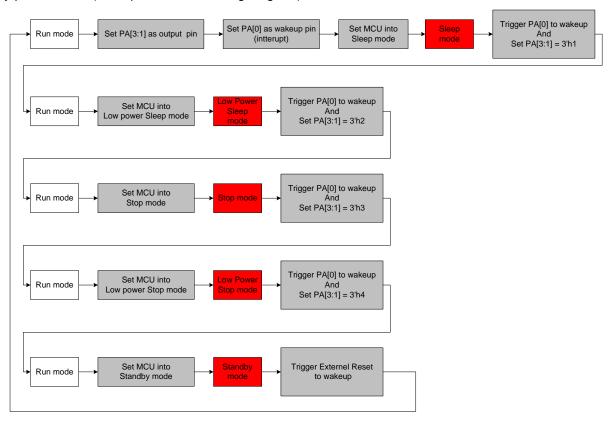

|      | 5.5                | Power Saving Mode                                 |     |  |  |

|      |                    | 5.5.1 Extended Interrupt (EXTI) for wake up       |     |  |  |

|      | F 6                | <b>9</b>                                          |     |  |  |

|      | 5.6<br>5.7         | Register Definition                               |     |  |  |

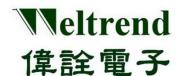

|      | 5.1                | 5.7.1 Run mode                                    |     |  |  |

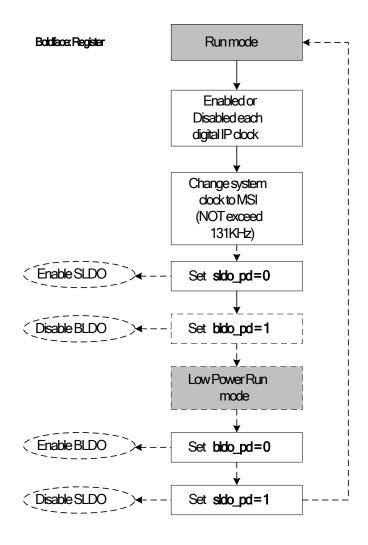

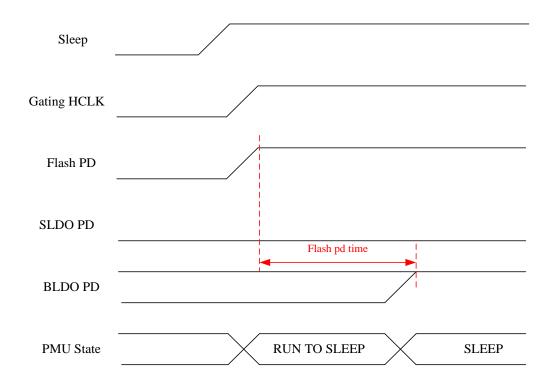

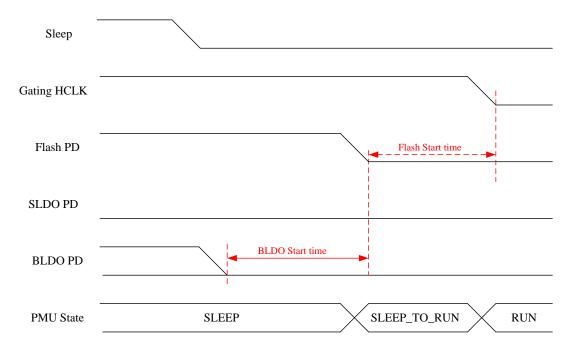

|      |                    | 5.7.2 Sleep Mode                                  |     |  |  |

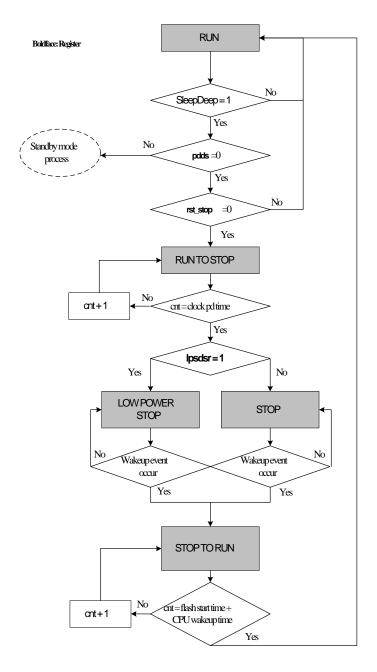

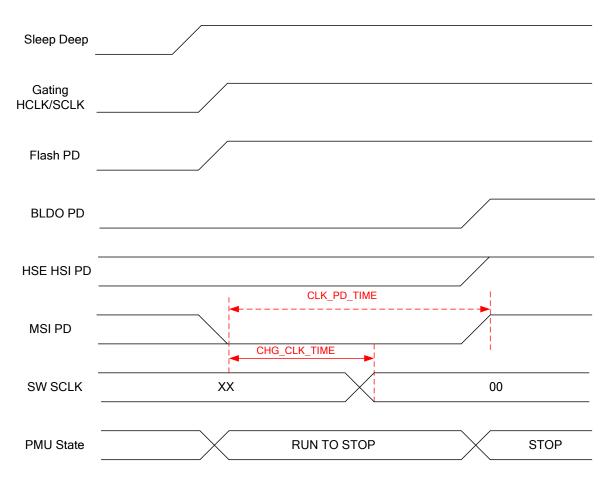

|      |                    | 5.7.3 Stop mode                                   |     |  |  |

|      |                    | 5.7.4 Standby mode                                |     |  |  |

|      | 5.8                | ,                                                 | 50  |  |  |

|      | 5.9                | Operating mode & Wake up Source                   |     |  |  |

| 6 | eFlas |          | rol                                                               | •  |

|---|-------|----------|-------------------------------------------------------------------|----|

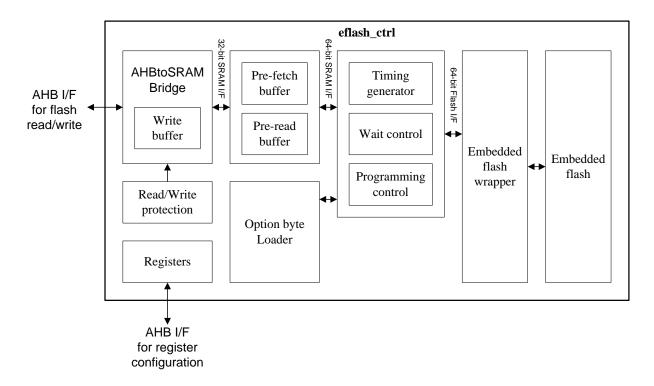

|   | 6.1   | Main F   | eatures                                                           | 52 |

|   | 6.2   | Block [  | Diagram                                                           | 52 |

|   | 6.3   | Registe  | er Definition                                                     | 53 |

|   | 6.4   | Function | onal Description                                                  | 58 |

|   |       | 6.4.1    | NVM Functional Description                                        |    |

|   |       | 6.4.2    | Reading the NVM                                                   | 58 |

|   |       | 6.4.3    | Writing/Erasing the NVM                                           | 62 |

|   |       | 6.4.4    | Unlocking/Locking Operations                                      |    |

|   |       | 6.4.5    | Status Register                                                   |    |

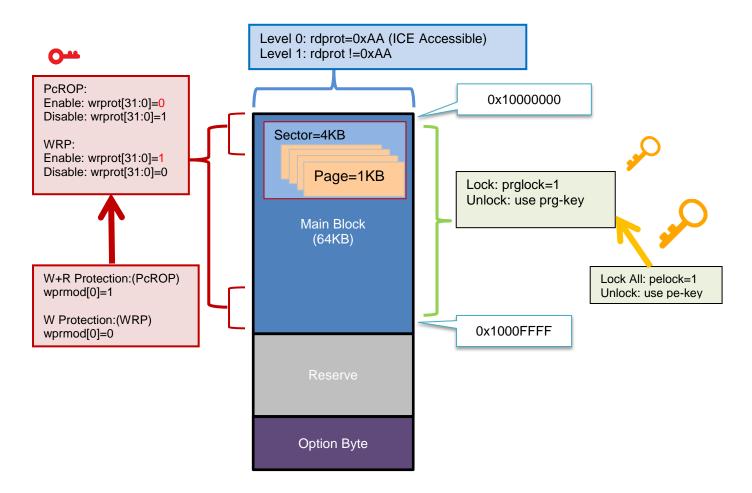

|   | 6.5   | Memor    | ry Protection                                                     |    |

|   |       | 6.5.1    | RDP (Read Out Protection)                                         |    |

|   |       | 6.5.2    | PcROP (Proprietary Code Read-Out Protection)                      | 66 |

|   |       | 6.5.3    | Protections Against unwanted Write/Erase Operations               | 67 |

|   |       | 6.5.4    | Reading the NVM                                                   | 68 |

|   |       | 6.5.5    | Protection Errors                                                 |    |

|   | 6.6   |          | nterrupts                                                         |    |

|   |       | 6.6.1    | Hard Fault                                                        |    |

|   | 6.7   | Memor    | ry Interface Management                                           |    |

|   | •     | 6.7.1    | Operation Priority and Evolution                                  |    |

|   |       | 6.7.2    | Sequence of Operations                                            |    |

|   |       | 6.7.3    | Change the Number of Wait-States while Reading                    | 70 |

|   | 6.8   |          | Bytes                                                             |    |

|   | 0.0   | 6.8.1    | API for Option Bytes                                              |    |

|   |       | 6.8.2    | Mismatch when loading protection flags                            |    |

|   |       | 6.8.3    | Simulated EEPROM                                                  |    |

|   |       | 0.0.0    | 6.8.3.1 Description                                               |    |

| _ |       |          | ·                                                                 |    |

| 7 |       |          |                                                                   |    |

|   | 7.1   |          | es                                                                |    |

|   | 7.2   |          | on description                                                    |    |

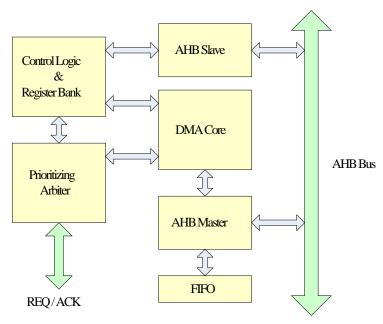

|   |       | 7.2.1    | Block Diagram                                                     |    |

|   |       | 7.2.2    | AHB Master Interface                                              |    |

|   |       | 7.2.3    | AHB Slave Interface                                               |    |

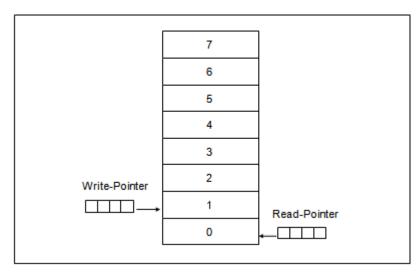

|   |       | 7.2.4    | FIFO Buffer                                                       |    |

|   |       | 7.2.5    | DMA Core                                                          |    |

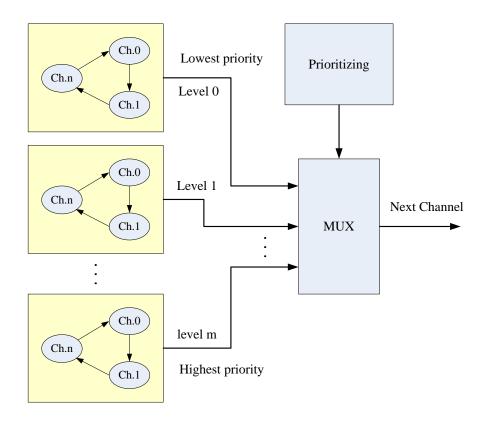

|   |       | 7.2.6    | Prioritizing Arbiter                                              |    |

|   |       | 7.2.7    | Control Logic & Register bank                                     |    |

|   | 7.3   | DMA R    | Register Table                                                    |    |

|   |       | 7.3.1    | Ciosal Colling for interrupt claracy cream, Chamber 200, imminint | 75 |

|   |       | 7.3.2    | DMA Channel x source AddrESS register                             |    |

|   |       | 7.3.3    | DMA channel x destination address register                        |    |

|   |       | 7.3.4    | DMA channel x number of data register                             |    |

|   |       | 7.3.5    | DMA channel x configuration register                              | 80 |

| 8 | GPIO  | ,        |                                                                   | 86 |

| U | 8.1   |          | eatures                                                           |    |

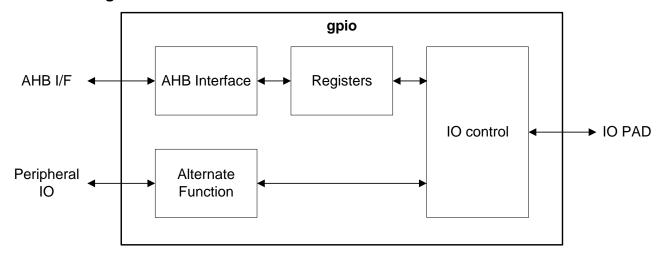

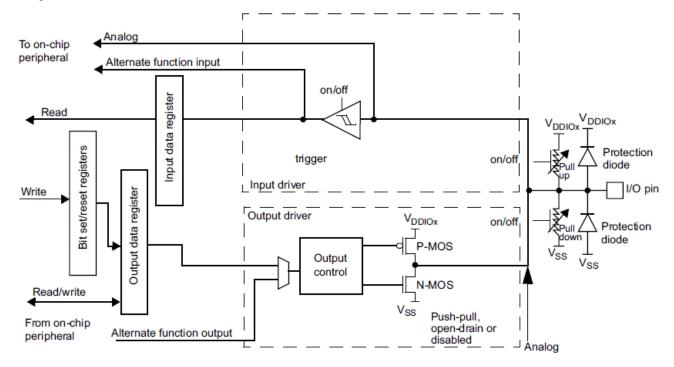

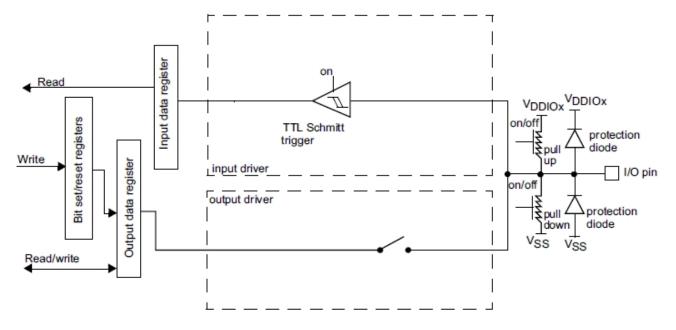

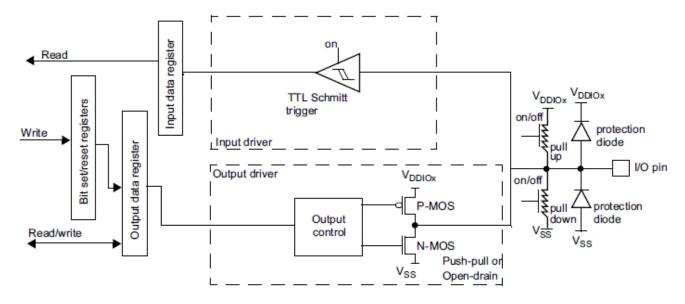

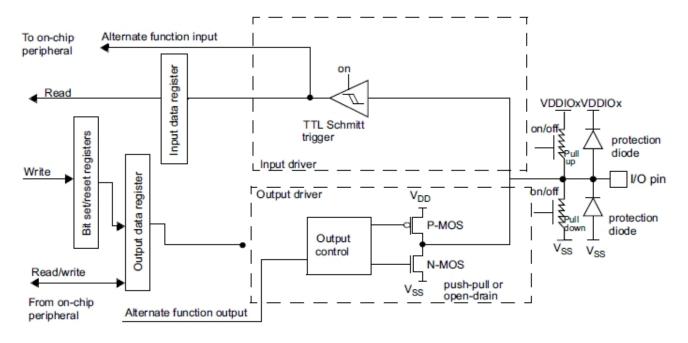

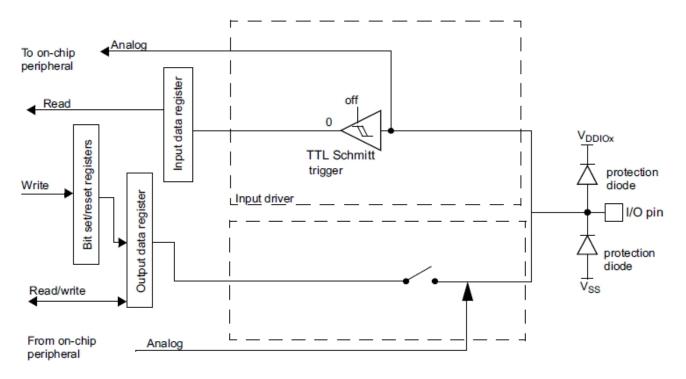

|   | 8.2   |          | Diagram                                                           |    |

|   | 8.3   |          | er Definition                                                     |    |

|   | 8.4   |          | onal Description                                                  |    |

|   | 0.4   | 8.4.1    | General-purpose I/O                                               |    |

|   |       | 8.4.2    | General-purpose I/O                                               |    |

|   |       | 8.4.3    | I/O port control registers                                        |    |

|   |       | 8.4.4    | •                                                                 |    |

|   |       |          | I/O port data registers I/O data bitwise handling                 |    |

|   |       | 8.4.5    |                                                                   |    |

|   |       | 8.4.6    | I/O alternate function input/output                               | 90 |

|    |        | 8.4.7   | Input configuration                               | 98  |

|----|--------|---------|---------------------------------------------------|-----|

|    |        | 8.4.8   | Output configuration                              |     |

|    |        | 8.4.9   | Alternate function configuration                  | 100 |

|    |        | 8.4.10  |                                                   |     |

|    |        | 8.4.11  | Using the HXTAL or LXTAL oscillator pins as GPIOs | 102 |

| 9  | USB.   |         |                                                   |     |

|    | 9.1    |         | eatures                                           |     |

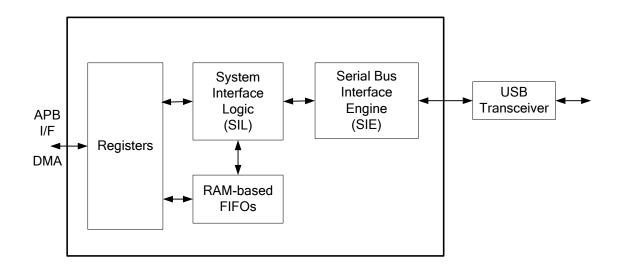

|    | 9.2    | Block D | Diagram                                           | 103 |

|    | 9.3    | Registe | er Definition                                     | 104 |

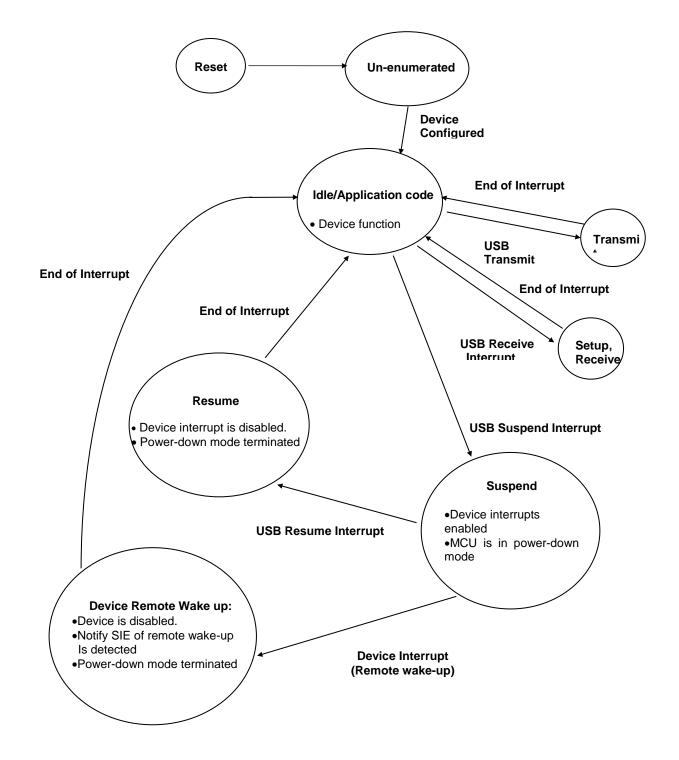

|    | 9.4    | Functio | n Description                                     | 115 |

|    |        | 9.4.1   | Main blocks                                       | 115 |

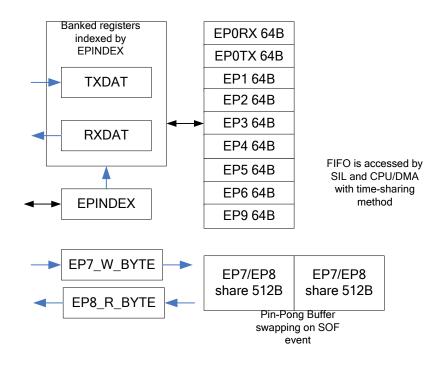

|    |        | 9.4.2   | Function endpoints                                | 116 |

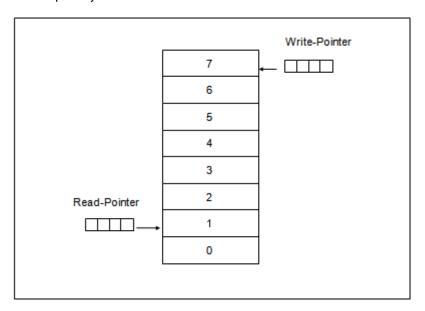

|    |        | 9.4.3   | Transmit FIFOs                                    | 116 |

|    |        |         | 9.4.3.1 Transmit FIFOs Features                   | 116 |

|    |        |         | 9.4.3.2 Transmit Data Set Management              |     |

|    |        | 9.4.4   | Receive FIFOs                                     |     |

|    |        |         | 9.4.4.1 Receive FIFOs Features                    |     |

|    |        |         | 9.4.4.2 Receive Data Set Management               |     |

|    |        | 9.4.5   | Setup Token Receive FIFO Handling                 |     |

|    |        | 9.4.6   | Suspend and Resume                                |     |

|    |        | 9.4.7   | FIFO memory address mapping                       |     |

| 40 | Ola al |         | ery System                                        |     |

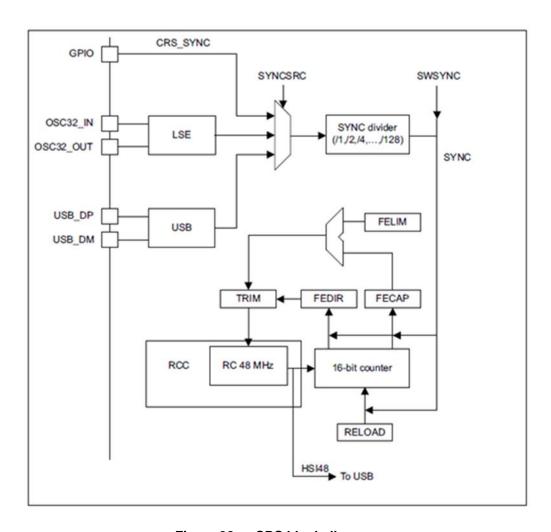

| 10 |        |         |                                                   |     |

|    |        |         | eatures                                           |     |

|    |        |         | Diagram                                           |     |

|    | 10.3   |         | er Definition                                     |     |

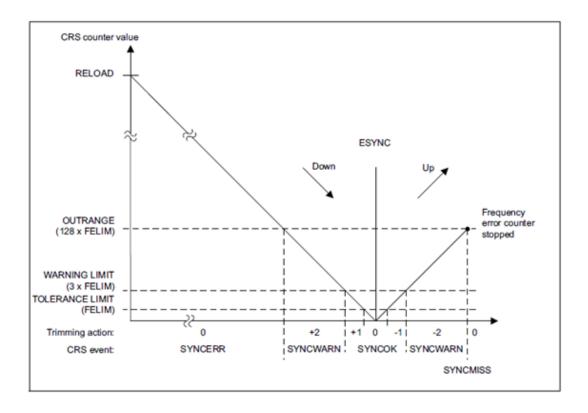

|    | 10.4   |         | onal Description                                  |     |

|    |        | 10.4.1  | -7                                                |     |

|    |        |         | Frequency error measurement                       |     |

|    |        |         | Frequency error evaluation and automatic trimming |     |

|    |        |         | CRS initialization and configuration              |     |

|    |        |         | CRS low-power modes                               |     |

|    |        |         | CRS interrupts                                    |     |

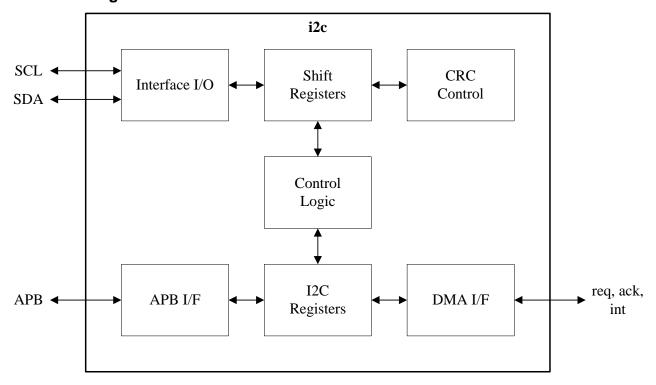

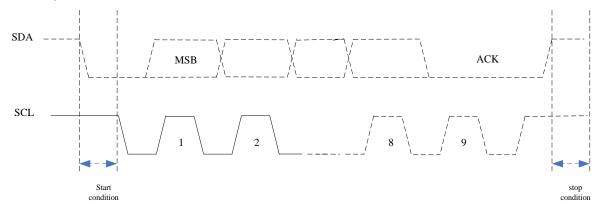

| 11 | _      |         |                                                   | _   |

|    |        |         | eatures                                           |     |

|    |        |         | Diagram                                           |     |

|    | 11.3   |         | er Definition                                     |     |

|    | 11.4   | Functio | nal Description                                   | 136 |

|    |        | 11.4.1  | Mode Selection                                    | 136 |

|    |        |         | 11.4.1.1 Communication Flow                       |     |

|    |        | 11.4.2  | I2C initialization                                |     |

|    |        |         | 11.4.2.1 Noise filter                             |     |

|    |        |         | 11.4.2.2 Timing                                   | 137 |

|    |        |         | 11.4.2.3 Software reset                           | 137 |

|    |        | 11.4.3  | Data transfer                                     | 137 |

|    |        |         | 11.4.3.1 Reception                                | 137 |

|    |        |         | 11.4.3.2 Transmission                             | 137 |

|    |        |         | 11.4.3.3 Hardware transfer management             | 137 |

|    |        | 11.4.4  | I2C Slave Mode                                    | 139 |

|    |        | 11.4.5  | I2C Master Mode                                   | 140 |

|    |        |         | 11.4.5.1 Communication Initialization             |     |

|    |        |         | 11.4.5.2 Master Transmitter                       |     |

|    |        |         | 11.4.5.3 Master Receiver                          |     |

|    |        | 11.4.6  | DMA requests                                      |     |

|    | 11.4.6.1 Transmission using DMA              |     |

|----|----------------------------------------------|-----|

|    | ·                                            |     |

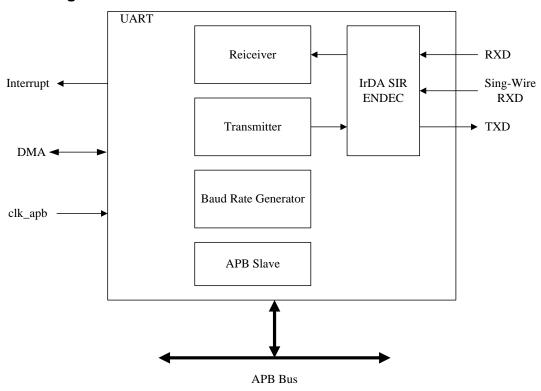

| 12 | UART                                         |     |

|    | 12.1 Main Features                           |     |

|    | 12.2 Block Diagram                           |     |

|    | 12.3 Register Definition                     |     |

|    | 12.4.1 Fractional baud rate generation       |     |

|    | 12.4.1 Practional baud rate generation       |     |

|    | 12.4.3 Parity control                        |     |

|    | 12.4.4 Single-wire half-duplex communication |     |

| 12 | SPI                                          |     |

| 13 | 13.1 Main Features                           |     |

|    | 13.2 Block Diagram                           |     |

|    | 13.3 Register Definition                     |     |

|    | 13.4 Functional Description                  |     |

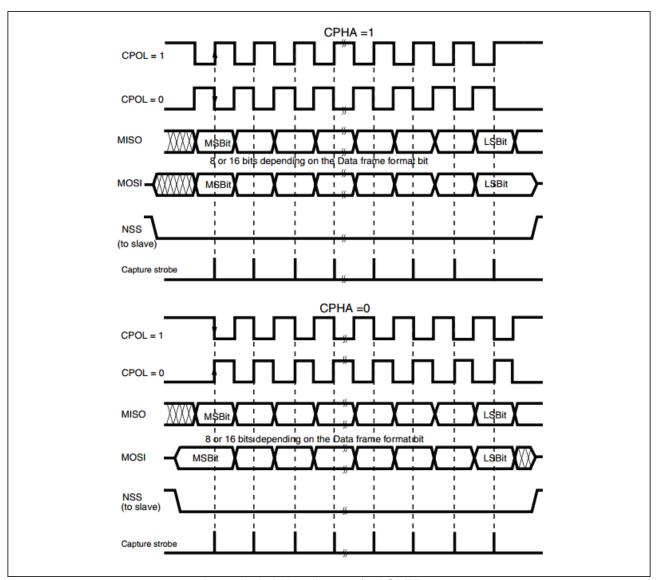

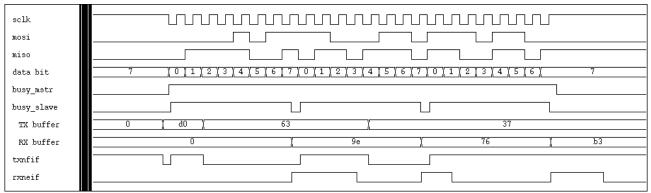

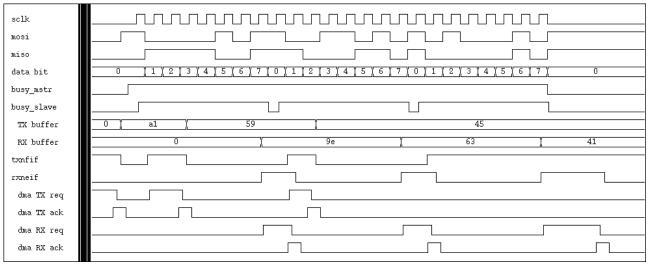

|    | 13.5 SPI Timing Diagram                      |     |

|    |                                              |     |

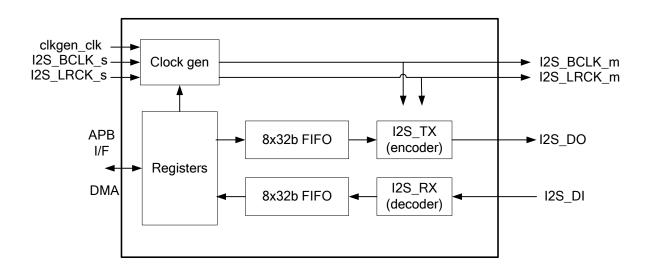

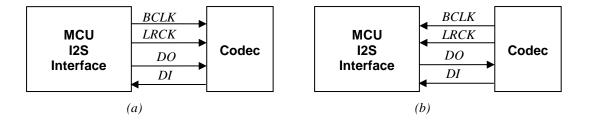

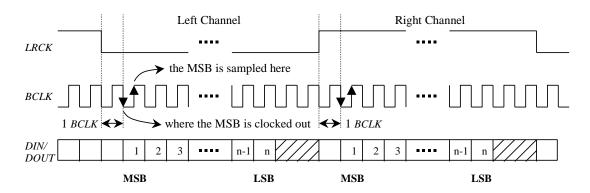

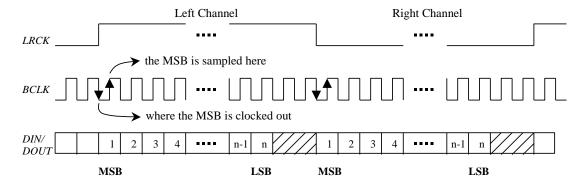

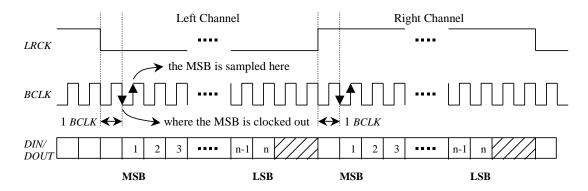

| 14 | 12S                                          |     |

|    | 14.1 Main Features                           |     |

|    | 14.2 Block Diagram                           |     |

|    | 14.4 Functional Description                  |     |

|    | 14.4.1 The Basics of I2S Bus                 |     |

|    | 14.4.2 Left Justified Mode                   |     |

|    | 14.4.3 I2S Mode                              |     |

|    | 14.4.4 I2S Clock Generation                  |     |

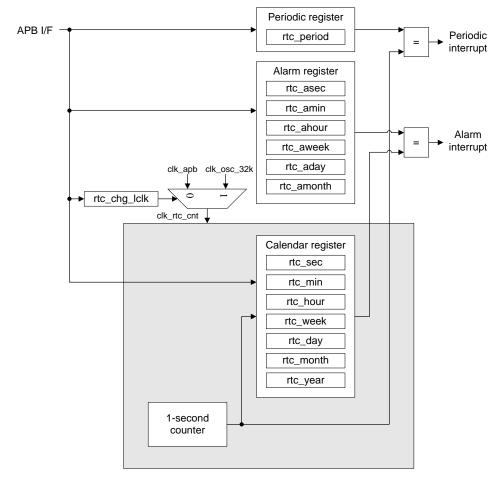

| 15 | Real-Time Clock                              | 165 |

|    | 15.1 Main Features                           |     |

|    | 15.2 Block Diagram                           |     |

|    | 15.3 Register Definition                     |     |

|    | 15.4 Functional Description                  |     |

|    | 15.4.1 Programmable Alarm                    |     |

|    | 15.4.2 Periodic Interrupt                    |     |

| 16 | Independent Watchdog Timer                   | 160 |

| 10 | 16.1 Main Features                           |     |

|    | 16.2 Block Diagram                           |     |

|    | 16.3 Register Definition                     |     |

|    | 16.4 Functional Description                  |     |

| 4- | ·                                            |     |

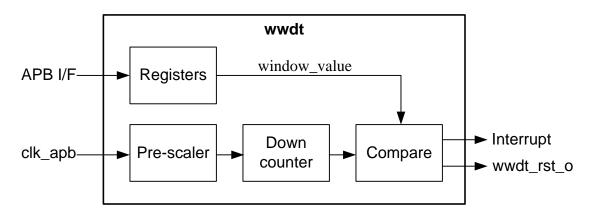

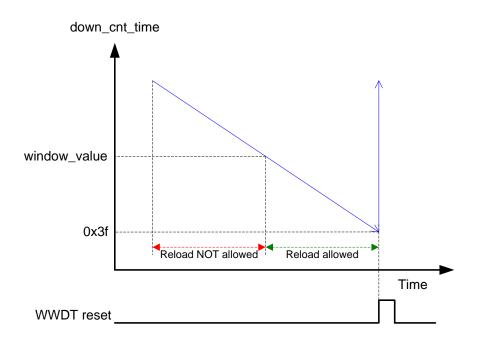

| 1/ | Window Watchdog Timer                        |     |

|    | 17.1 Main Features                           |     |

|    | 17.2 Block Diagram                           |     |

|    | 17.3 Register Definition                     |     |

|    | ·                                            |     |

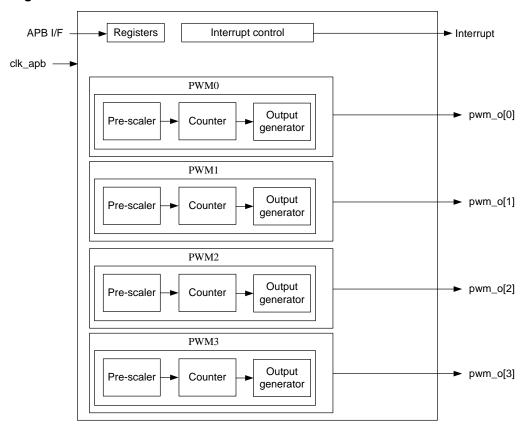

| 18 | PWM                                          |     |

|    | 18.1 Main Features                           |     |

|    | 18.2 Register Definition                     |     |

|    | 18.3 Functional Description                  |     |

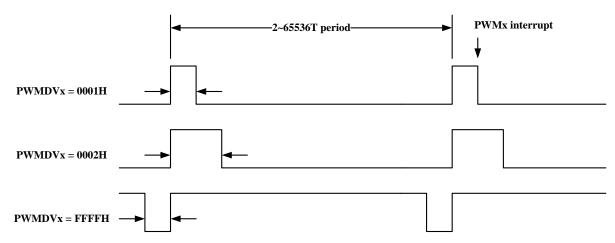

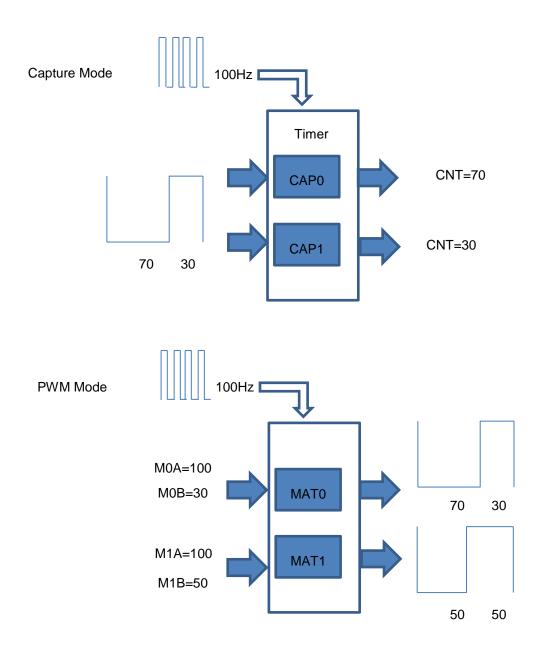

|    | 18.3.1 Independent PWM                       | 178 |

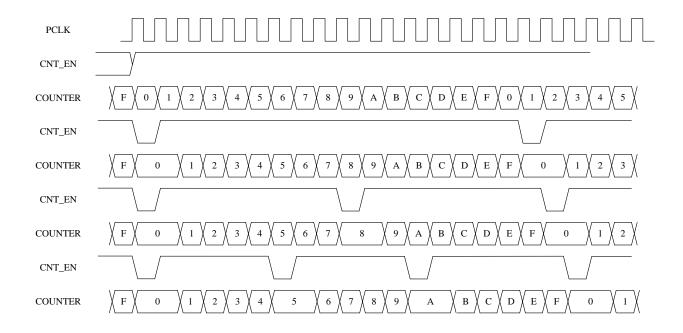

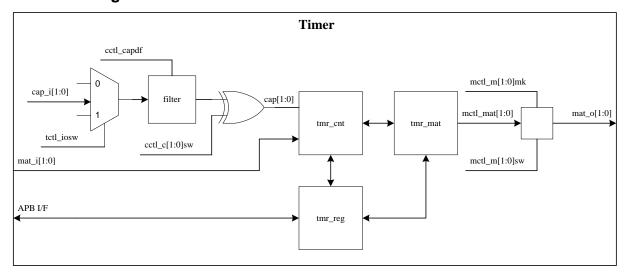

| 19 |                                              |     |

|    | 19.1 Main Features                           | 179 |

|    | 19.2 Block Diagram                           |     |

|    |       | Register DefinitionFunctional Description       | 186 |

|----|-------|-------------------------------------------------|-----|

|    |       | 19.4.1 Multiple Capture and Match Pins          |     |

|    |       | 19.4.2 Interrupts                               | 186 |

|    |       | 19.4.3 DMA                                      |     |

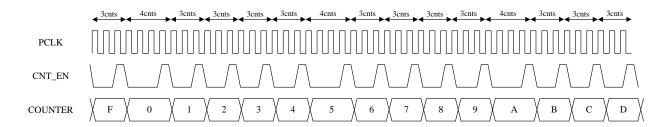

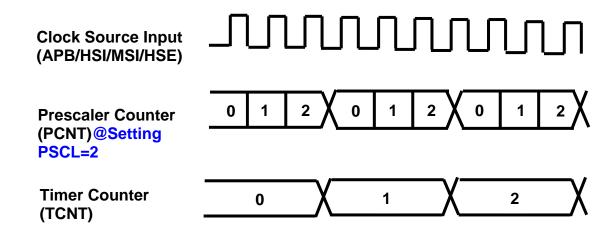

|    |       | 19.4.4 Count Control                            |     |

|    |       | 19.4.5 Capture Control                          |     |

|    |       | 19.4.6 Match Control                            | 187 |

| 20 | ۸DC   |                                                 | 1ΩΩ |

| 20 |       | Main Features                                   |     |

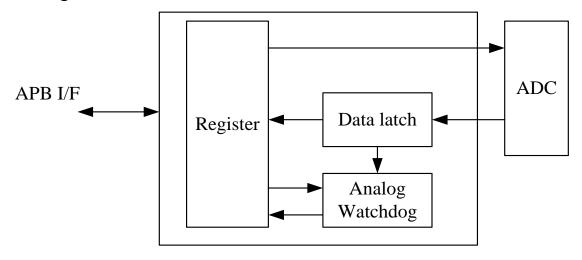

|    |       | Block Diagram                                   |     |

|    |       | Register Definition                             |     |

|    |       |                                                 |     |

|    | 20.4  | Functional Description                          |     |

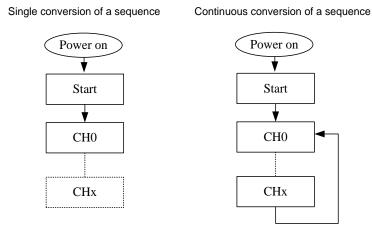

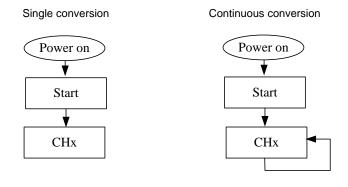

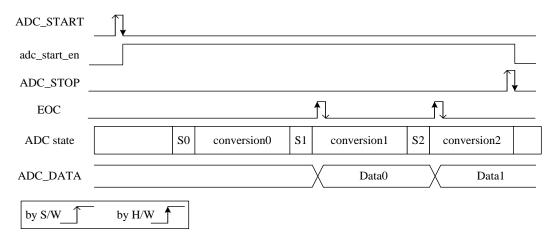

|    |       | 20.4.1 Conversion function                      |     |

|    |       |                                                 |     |

|    |       | 20.4.1.2 ADC_SLOW=1, When ADC clock > APB clock |     |

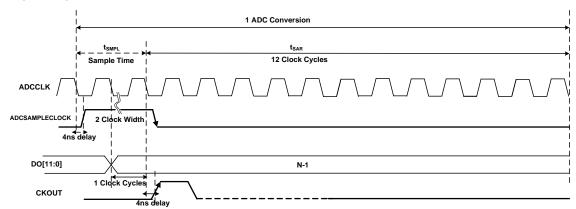

|    |       | 20.4.2 Conversion timing                        |     |

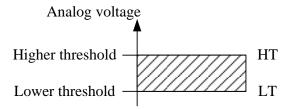

|    |       | 20.4.3 Analog Watchdog Window                   | 192 |

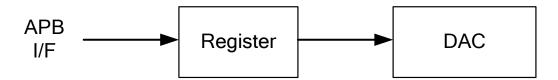

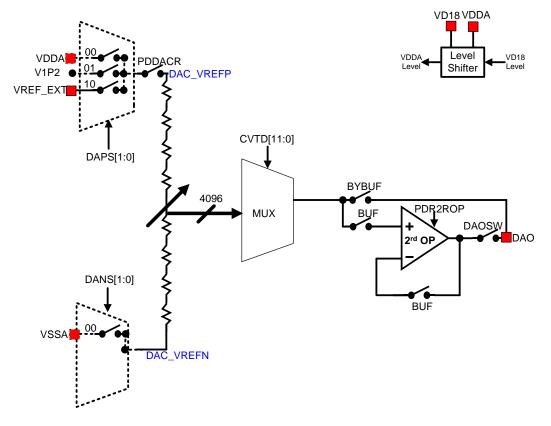

| 21 | DAC.  |                                                 | 193 |

|    | 21.1  | Main Features                                   | 193 |

|    | 21.2  | Block Diagram                                   | 193 |

|    | 21.3  | Register Definition                             | 194 |

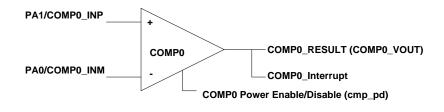

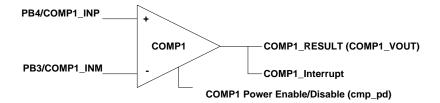

| 22 | 1 114 | Low Power Comparators                           | 40E |

| 22 |       |                                                 |     |

|    | 22.1  | Main Features                                   | 195 |

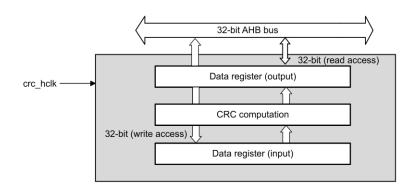

| 23 | CRC3  | 2                                               | 196 |

|    | 23.1  | Main Features                                   | 196 |

|    | 23.2  | Register Definition                             | 196 |

|    |       | Functional Description                          |     |

|    | 23.4  | CRC32 example code: using WT32L064/032          | 197 |

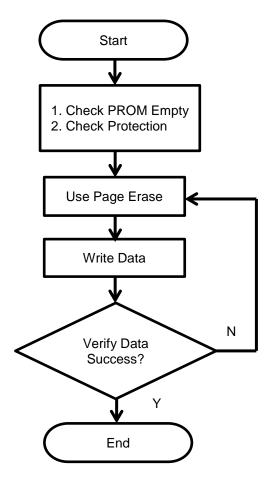

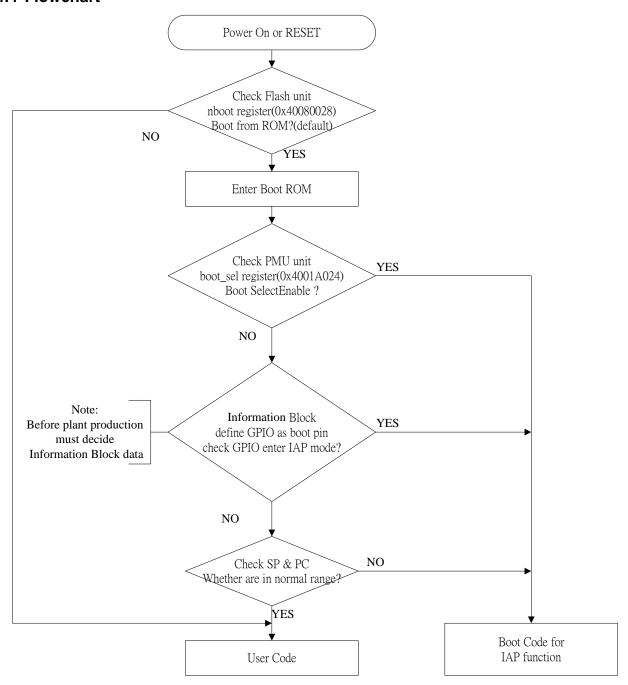

| 24 | Poot  | ROM & IAP                                       | 200 |

| 24 | 24.1  | Introduction                                    |     |

|    |       | How to enter the IAP                            |     |

|    |       |                                                 |     |

|    |       | Boot & IAP Memory Mapping                       |     |

|    | 24.4  | Flowchart                                       | 202 |

| 25 | Elect | ical Characteristics                            | 203 |

|    | 25.1  | Absolute Maximum Ratings                        | 203 |

|    | 25.2  | DC Characteristics                              | 204 |

|    |       | 25.2.1 Power consumption                        | 204 |

|    |       | 25.2.2 Digital I/O Characteristics              | 205 |

|    |       | 25.2.3 LVR Characteristics                      | 206 |

|    |       | 25.2.4 PLL Characteristics                      | 206 |

|    |       | 25.2.5 ADC Characteristics                      | 207 |

|    |       | 25.2.6 DAC Characteristics                      | 208 |

|    |       | 25.2.7 LDO Characteristics                      | 208 |

|    |       | 25.2.8 HSI 16MHz                                | 209 |

|    |       | 25.2.9 MSI 4.2MHz                               |     |

|    |       | 25.2.10 IRC48MHz Characteristics                |     |

|    |       | 25.2.11 IRC37kHz Characteristics                |     |

|    |       | 25.2.12 Crystal 32768 Characteristics           | 211 |

|    |       | 25.2.13 CMP Characteristics                     |     |

|    |       | 25.2.14 BOR/PVD Characteristics                 | 213 |

|    |       | 20.2.14 DOTAL VD OHAIAGIGHSIIGS                 |     |

# Weltrend 偉詮電子

## WT32L064/032

## Flash Memory Type 32-bit MCU

| 31 | Revision History                    | 227 |

|----|-------------------------------------|-----|

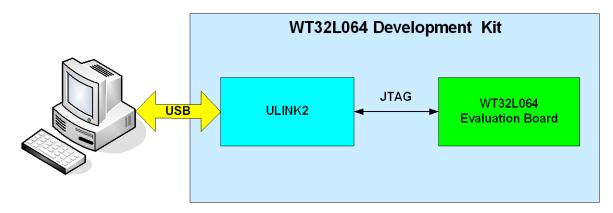

| 30 | Development Tool                    | 226 |

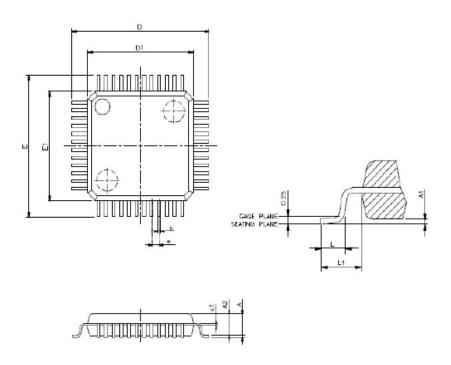

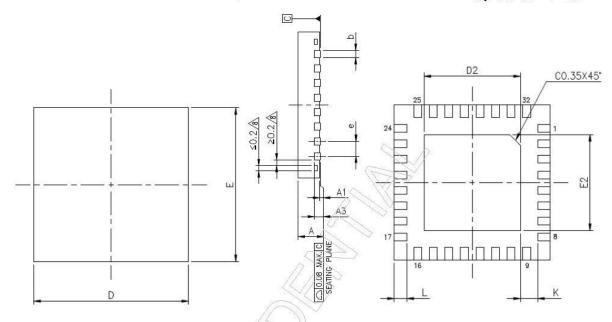

|    | 29.3 QFN-32 Outline Drawing         |     |

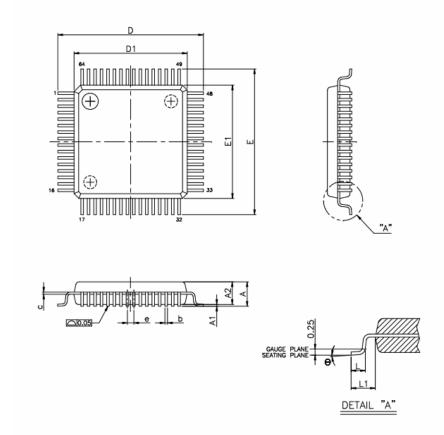

|    | 29.1 LQFP-64 Outline Drawing        |     |

| 29 | Package Outline Drawing             | 223 |

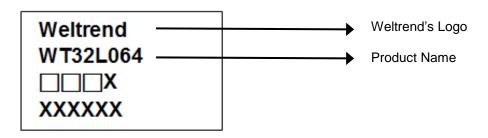

|    | 28.2.1 Top Marking – LQFP64/48      |     |

|    | 28.2 WT32L032                       | 222 |

|    | 28.1.2 Top Marking – QFN32          |     |

|    | 28.1.1 Top Marking – LQFP64/48      | 221 |

|    | 28.1 WT32L064                       |     |

| 28 | Ordering Information                | 221 |

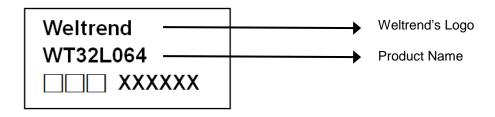

| 27 | Product Naming Rule                 | 220 |

|    | 26.4 VBAT & VDD33 dual power supply | 219 |

|    | 26.3 USB VBus 5V power supply       |     |

|    | 26.2 VDDBat power supply            |     |

| 26 | Application Circuit                 |     |

|    |                                     |     |

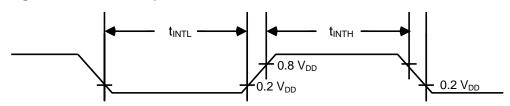

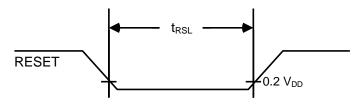

|    | 25.3 AC Characteristics             |     |

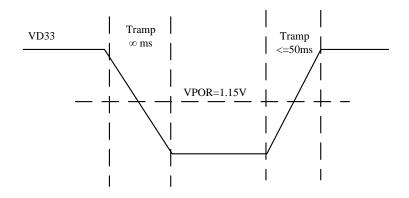

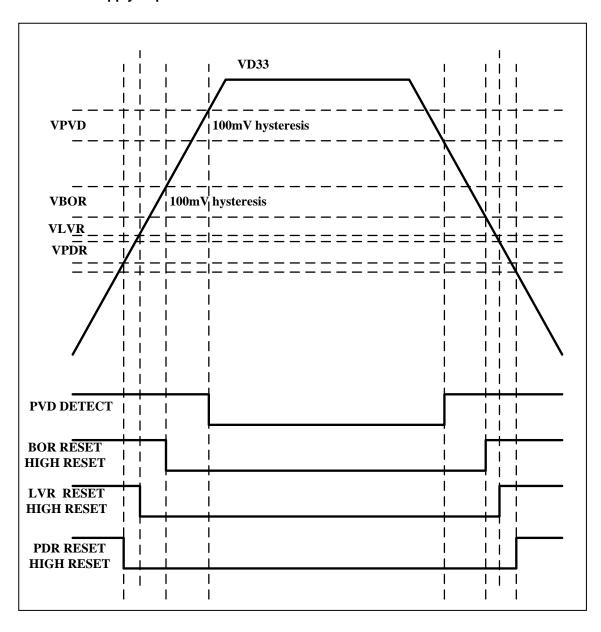

|    | 25.2.16 POWER Supply Supervisors    |     |

## Flash Memory Type 32-bit MCU

## **List of Figures**

| 6<br>8<br>10 |

|--------------|

|              |

|              |

| 10<br>22     |

| 22           |

|              |

| 23           |

|              |

| 31           |

| 32           |

| 40           |

| 41           |

| 42           |

| 43           |

| 44           |

| 45           |

| 46           |

| 47           |

| 48           |

| 49           |

| 50           |

| 52           |

| 60           |

| 65           |

| 74           |

| 86           |

| 96           |

| 99           |

| 100          |

| 101          |

| 102          |

| 103          |

| 104          |

| 116          |

| 118          |

| 121          |

| 124          |

| 126          |

| 130          |

| 136          |

| 144          |

| 148          |

| 151          |

| 159          |

| 161          |

| 162          |

| 162          |

|              |

# Weltrend 偉詮電子

## WT32L064/032

## Flash Memory Type 32-bit MCU

| Figure 49 | I2S mode timing diagram of I2S interface | 163 |

|-----------|------------------------------------------|-----|

| Figure 50 | RTC Block Diagram                        | 165 |

| Figure 51 | IWDT Block Diagram                       | 169 |

| Figure 52 | WWDT Block Diagram                       | 172 |

| Figure 53 | Timing Diagram of WWDT                   | 174 |

| Figure 54 | PWM Block Diagram                        | 175 |

| Figure 55 | PWM0~3 Function                          | 178 |

| Figure 56 | Timer Module Block Diagram               | 180 |

| Figure 57 | ADC Block Diagram                        | 188 |

| Figure 58 | Conversion of a Sequence by ADC_SLOW=0   | 191 |

| Figure 59 | Conversion by ADC_SLOW=1                 | 191 |

|           | ADC Conversion Time                      |     |

| Figure 61 | Timing Diagram by ADC_SLOW=0             | 192 |

|           | Analog Watchdog Window                   |     |

| Figure 63 | DAC Block Diagram                        | 193 |

| Figure 64 | DAC Analog Block Diagram                 | 193 |

| Figure 65 | WT32L064/032 Development Kit             | 226 |

#### **List of Tables**

| rable 1              | W132L064/032 Interrupt and Exception Vectors              | 9     |

|----------------------|-----------------------------------------------------------|-------|

| Table 2              | Pin Count Table                                           | 14    |

| Table 3              | Pin Assignment Table                                      | 15    |

| Table 4              | RCC Control Register                                      | 24    |

| Table 5              | Performance versus V <sub>CORE</sub> Ranges               | 33    |

| Table 6              | Summary of Saving Power Modes                             |       |

| Table 7              | EXTI Lines Connections                                    |       |

| Table 8              | PMU Control Register                                      |       |

| Table 9              | Peripherals on the Operating Mode                         |       |

| Table 10             | eFlash Control Register Table                             |       |

| Table 11             | NVM organization                                          |       |

| Table 12             | Number of wait states                                     |       |

| Table 13             | Pre-fetch & Pre-buffer Management                         |       |

| Table 14             | Configurations for buffers and speculative reading        |       |

| Table 15             | PcROP & wrprot Flash Memory Protected Range               |       |

| Table 16             | Memory access vs mode                                     |       |

| Table 17             | Flash interrupt request                                   |       |

| Table 18             | API Functions                                             |       |

| Table 19             | GPIO Control Register                                     |       |

| Table 20             | USB Control Register                                      |       |

| Table 20             | Writing to the Byte Count Register                        |       |

| Table 21             | Truth Table for Transmit FIFO Management                  |       |

| Table 22             | Status of the Receive FIFO Data Set                       |       |

| Table 23             | Truth Table for Receive FIFO Management                   |       |

| Table 25             | FIFO Memory Address Mapping                               |       |

| Table 25             | CRS Control Register                                      |       |

| Table 20             | Effect of Low-Power Modes on CRS                          |       |

| Table 27             | CRS Interrupt Control Bits                                |       |

|                      | I2C Control Register                                      |       |

| Table 29             | UART Control Register                                     |       |

| Table 30             | UART Baud Rate Table                                      |       |

| Table 31<br>Table 32 | UART Noise Error                                          |       |

|                      |                                                           |       |

| Table 33:            | Parity control table                                      |       |

| Table 34             | SPI Control Register                                      |       |

| Table 35             | I2S Control Register                                      |       |

| Table 36             | I2S Sampling Rate                                         |       |

| Table 37             | I2S System Clock = 24MHz (assume f <sub>BCLK</sub> =64fs) |       |

| Table 38             | I2S System Clock = 12MHz (assume f <sub>BCLK</sub> =64fs) |       |

| Table 39             | RTC Control Register                                      |       |

| Table 40             | IWDT Control Register                                     |       |

| Table 41             | IWDT Min./Max. Timeout Period at 37 kHz Clock Input       |       |

| Table 42             | WWDT Control Register                                     |       |

| Table 43             | WWDT Min./Max Timeout Value at 24.00MHz                   |       |

| Table 44             | PWM Control Register                                      |       |

| Table 45             | Timer Control Register                                    |       |

| Table 46             | ADC Control Register                                      |       |

| Table 47             | DAC Control Register                                      |       |

| Table 48             | CRC32 Control Register                                    | . 196 |

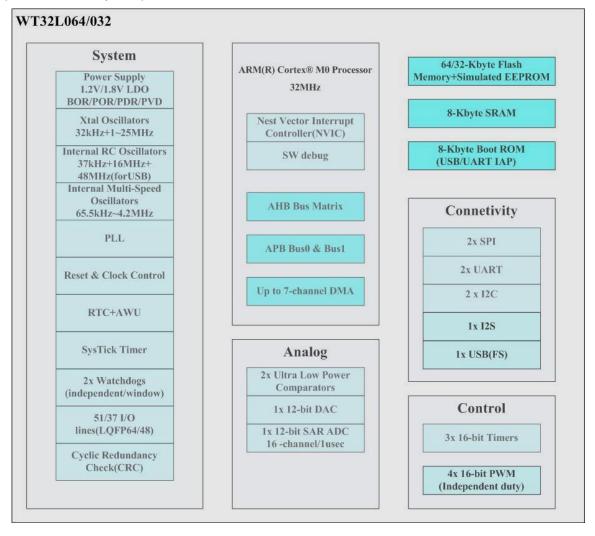

#### 1 General Description

The WT32L064/032 is an ultra-low power Arm Cortex M0-based 32-bit microcontroller with 64KB/32KB embedded flash memory and 8KB SRAM. It could operate up to 32MHz and is able to achieve 32 MIPS performance due to the advanced design by Weltrend, where zero wait-state can be obtained while accessing flash memory.

In addition, with low power design technique and extremely low leakage semiconductor process technology, the power consumption of WT32L064/032 can be less than  $0.6\mu A$  in stop mode and less than  $0.3\mu A$  in standby mode.

This highly integrated MCU contains rich peripherals such as 12-bit ADC, 12-bit DAC, CRC32, GPIO, PWM, USB2.0, I2S, I2C, UART, SPI, and etc., which is perfectly suitable for battery-powered and energy harvesting applications.

Some examples of the applications of the WT32L064/032 include True Wireless Stereo (TWS) charging case, dual-mode wireless gaming keyboard and mouse, flowmeter, various sensor applications such as gas, temperature, humidity and pressure sensor as well as sensor hub.

Figure 1 WT32L064/032 System Block Diagram

#### Flash Memory Type 32-bit MCU

#### 1.1 Main Features

- Ultra-low-power platform

- 1.65V to 3.6V power supply

- √ 1.65V~1.8V @Max.4.2 MHz (Flash read only)

- √ 1.8V~2.2V @Max.4.2 MHz (Flash read & write)

- √ 2.3V~3.6V @Max.32 MHz (Flash read & write)

- -40°C to 105°C temperature range

- 0.3 µA Standby mode

- 1.0 μA Standby mode with RTC on

- 0.6 µA Stop mode

- 1.3 µA Stop mode with RTC on

- Core: ARM<sup>®</sup> 32-bit Cortex<sup>®</sup>-M0 processor

- From 65.5 kHz up to 32 MHz Max.

- **0.88** DMIPS/MHz

- Interrupt Source

ARM Cortex-M0 built-in Nested Vectored Interrupt Controller (NVIC).

- 32 external interrupt inputs, each with four levels of priority

- Dedicated non-Maskable Interrupt (NMI) input

- Support for both level-sensitive and pulse-sensitive interrupt lines

- Wake-up Interrupt Controller (WIC), supports sleep mode

- System Tick Timer

- 24-bit timer clock is fixed to the frequency of the system clock

- Memories

- WT32L064: Up to 64 KB Flash memory

- WT32L032: Up to 32 KB Flash memory

- 8 KB SRAM

- Up to 51 fast I/Os (most 5V tolerant)

- Reset and supply management

- Ultra-safe, low-power BOR (brownout reset) with 5 selectable thresholds

- Ultra-low-power POR/PDR

- Programmable voltage detector (PVD)

- Clock sources

- 1 MHz to 25 MHz crystal oscillator

# Weltrend 偉詮電子

## WT32L064/032

#### Flash Memory Type 32-bit MCU

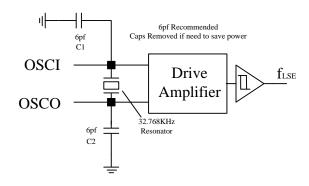

- 32 kHz oscillator for RTC and calendar function (Notice: RTC clock needs to be enabled first, please refer to RCC Table 4 for more details)

- High speed internal 16 MHz factory-trimmed RC (± 1%)

- Internal low-power 37 kHz RC

- Internal multispeed low-power 65 kHz to 4.2 MHz RC

- Internal self- calibration of 48 MHz RC for USB

- PLL for CPU clock

- Development support

- Serial wire debug supported

- Rich Analog peripherals

- 12-bit SAR ADC 0.5 Ms/s up to 16 channels (down to 1.8 V)

- 12-bit channel DACs with output buffers (down to 1.8 V)

- Ultra-low-power comparators (window mode and wake up capability, down to 1.65 V)

- 7-channel DMA controller, supporting ADC, SPI, I<sup>2</sup>C, UART, Timers, and USB

- Peripheral communication interfaces

- 1x USB 1.1 crystal-less

- 2x UART

- Up to 2x SPI 16 M bits/sec.

- 2x I2C

- 1x I2S up to 32-bit word size

- 6x timers: 3x 16-bit with up to 4 channels, 1x RTC and 2x Watchdogs (independent/window)

- 4-channel PWM

- CRC calculation unit

- Green package: LQFP-64 (7mmx7mm), LQFP-48 (7mmx7mm), and QFN32 (5mmx5mm)

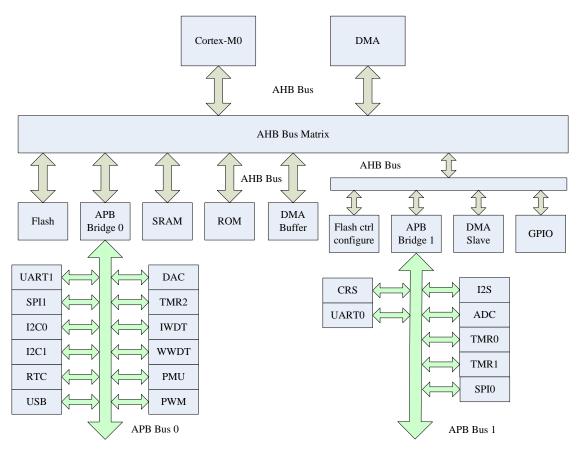

#### 1.2 System Block Diagram

Figure 2 System Block Diagram

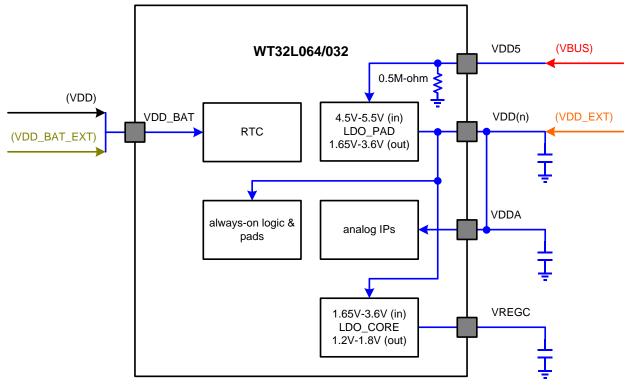

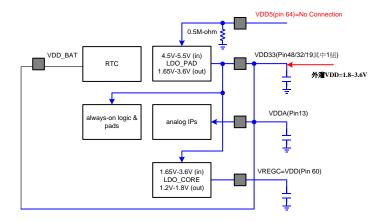

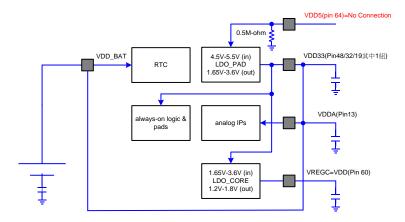

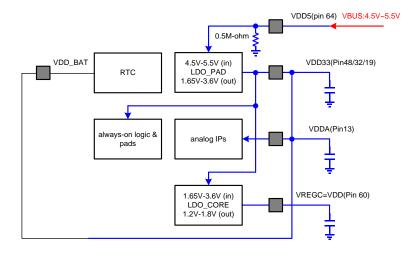

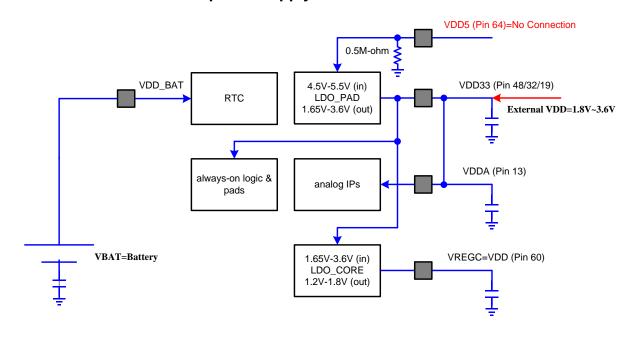

#### 1.3 System Power Architecture

#### Notes:

- 1. blue circuits are fixed

- 2. only one of VBUS or VDD\_EXT is supplied, the other is floating

- 3. only one of VDD or VDD\_BAT\_EXT is supplied for VDD\_BAT, the other is floating

Figure 3 System Power Architecture

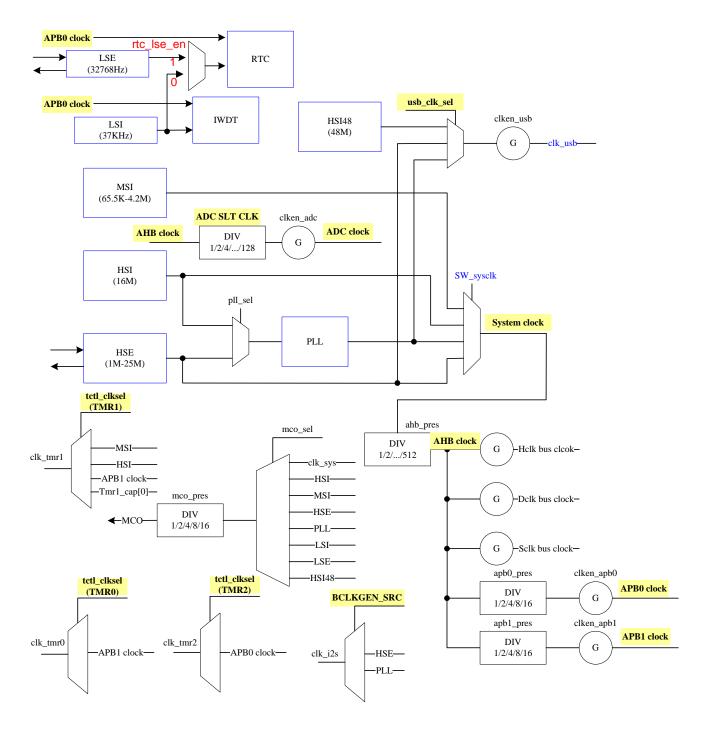

#### 1.4 System Clock Tree

Figure 4 System Clock Tree

#### 1.5 ARM<sup>®</sup> Cortex™-M0 Processor

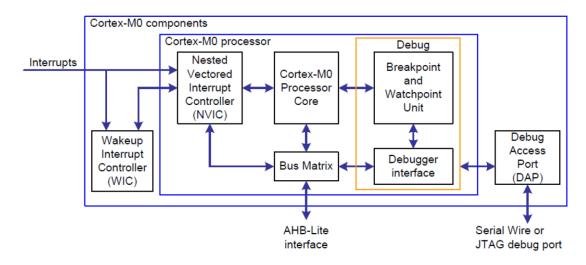

The Cortex™-M0 processor is a configurable, multistage, 32-bit RISC processor. It has an AMBA AHB-Lite interface and includes a NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex-M profile processor.

Figure 5 ARM® Cortex™-M0 Processor

#### 1.5.1 Cortex M0 Processor Features

- Cortex-M0 processor includes

- ✓ Cortex-M0 processor core

- ✓ Nested Vectored Interrupt Controller (NVIC)

- ✓ System Timer (SysTick)

- ARMv6-M Thumb instruction set

- NVIC: 32 external interrupt inputs

- Debug: 4 HD breakpoints, 2 watchpoints.

- Bus interfaces: 32-bit AMBA-3 AHB-Lite system interface

- ARMv6-M (which is a subset of ARMv7-M, upward compatible)

- It supports only the Thumb instruction set. No Interworking code is required.

- ✓ Total are 56 instructions. 6 are 32-bit length, the others are 16-bit length

- ✓ 32-bit instructions: BL, DMB, DSB, ISB, MRS, MSR

- Supports byte (8-bit), halfword (16-bit) and word (32-bit) data types, each must be accessed with natural alignment.

- Built-in timer and interrupt controller

- ✓ Systick, NVIC

- Memory mapped I/O

- ✓ Use same instructions to access memory and registers

- ✓ Ex: LDR, STR

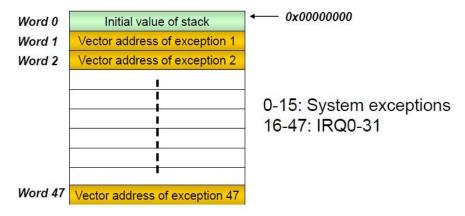

#### 1.5.2 Nested Vectored Interrupt Controller (NVIC)

Cortex-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)". It is closely coupled to the processor kernel and provides following features:

- Nested and Vectored interrupt support

- Automatic processor state saving and restoration

- Dynamic priority changing

- Reduced and deterministic interrupt latency

- An exception may be an interrupt or a hardware error

- Each exception has exception number, priority number and vector address

- √ Vector address

- ✓ Vector table base address is fixed at 0x00000000

Figure 6 Cortex M0 NVIC Vector

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports 32 (IRQ[31:0]) discrete interrupts with 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running priority. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler. Table1 shows WT32L064/032 interrupt and exception vectors.

Table 1 WT32L064/032 Interrupt and Exception Vectors

| Position Priority Type of priority |                                          | Acronym  | Description  | Address                                                                                  |             |

|------------------------------------|------------------------------------------|----------|--------------|------------------------------------------------------------------------------------------|-------------|

| -                                  | -                                        | -        | - Reserved ( |                                                                                          | 0x0000 0000 |

| -                                  | -3                                       | fixed    | Reset        | Reset                                                                                    | 0x0000 0004 |

| -                                  | -2                                       | fixed    | NMI          | Non maskable interrupt. The RCC Clock Security System (CSS) is linked to the NMI vector. | 0x0000 0008 |

| -                                  | -1                                       | fixed    | HardFault    | All class of fault                                                                       | 0x0000 000C |

| -                                  | 3                                        | settable | SVCall       | System service call via SWI instruction                                                  | 0x0000 002C |

| -                                  | 5                                        | settable | PendSV       | Pendable request for system service                                                      | 0x0000 0038 |

| -                                  | 6                                        | settable | SysTick      | System tick timer                                                                        | 0x0000 003C |

| 0                                  | 7                                        | settable | UART0        | UART0 global interrupt                                                                   | 0x0000 0040 |

| 1                                  | 8                                        | settable | UART1        | UART1 global interrupt                                                                   | 0x0000 0044 |

| 2                                  |                                          |          | Reserved     |                                                                                          | 0x0000 0048 |

| 3                                  | 10                                       | settable | I2C0         | I2C0 global interrupt                                                                    | 0x0000 004C |

| 4                                  | 11                                       | settable | I2C1         | I2C1 global interrupt                                                                    | 0x0000 0050 |

| 5                                  | 12                                       | settable | PWM          | PWM global interrupt                                                                     | 0x0000 0054 |

| 6                                  | 6 13 settable SPI0 SPI0 global interrupt |          | 0x0000 0058  |                                                                                          |             |

| 7                                  | 7 14 settable SPI1 SPI1 global interrupt |          | 0x0000 005C  |                                                                                          |             |

| 8                                  | 15                                       | settable | WWDT         | WWDT global interrupt                                                                    | 0x0000 0060 |

| 9                                  | 16                                       | settable | TMR0         | TMR0 global interrupt                                                                    | 0x0000 0064 |

| 10                                 | 17                                       | settable | TMR1         | TMR1 global interrupt                                                                    | 0x0000 0068 |

| 11                                 | 18                                       | settable | I2S_RX       | I2S RX global interrupt                                                                  | 0x0000 006C |

| 12                                 | 19                                       | settable | I2S_TX       | I2S TX global interrupt                                                                  | 0x0000 0070 |

| 13                                 | 20                                       | settable | USB0         | USB0 global interrupt                                                                    | 0x0000 0074 |

| 14                                 | 21                                       | settable | USB1         | USB1 global interrupt                                                                    | 0x0000 0078 |

| 15                                 | 22                                       | settable | ADC          | ADC global interrupt                                                                     | 0x0000 007C |

| 16                                 | 23                                       | settable | RTC          | RTC global interrupt                                                                     | 0x0000 0080 |

| 17                                 |                                          |          | Reserved     |                                                                                          | 0x0000 0084 |

| 18                                 | 25                                       | settable | CRS          | CRS global interrupt                                                                     | 0x0000 0088 |

| 19                                 | 26                                       | settable | TMR2         | TMR2 global interrupt                                                                    | 0x0000 008C |

| 20                                 | 27                                       | settable | PVD          | PVD global interrupt                                                                     | 0x0000 0090 |

| 21                                 | 28                                       | settable | CMP0         | CMP0 global interrupt                                                                    | 0x0000 0094 |

| 22                                 | 29                                       | settable | CMP1         | CMP1 global interrupt                                                                    | 0x0000 0098 |

| 23                                 | 30                                       | settable | eFlash_CTRL  | eFlash controller global interrupt                                                       | 0x0000 009C |

| 24                                 | 31                                       | settable | DMA0         | DMA channel 0 interrupt                                                                  | 0x0000 00A0 |

#### Flash Memory Type 32-bit MCU

| Position | Priority | Type of priority | Acronym | Description             | Address     |

|----------|----------|------------------|---------|-------------------------|-------------|

| 25       | 32       | settable         | DMA1    | DMA channel 1 interrupt | 0x0000 00A4 |

| 26       | 33       | settable         | DMA2    | DMA channel 2 interrupt | 0x0000 00A8 |

| 27       | 34       | settable         | DMA3    | DMA channel 3 interrupt | 0x0000 00AC |

| 28       | 35       | settable         | DMA4    | DMA channel 4 interrupt | 0x0000 00B0 |

| 29       | 36       | settable         | DMA5    | DMA channel 5 interrupt | 0x0000 00B4 |

| 30       | 37       | settable         | DMA6    | DMA channel 6 interrupt | 0x0000 00B8 |

| 31       | 38       | settable         | GPIO    | GPIO global interrupt   | 0x0000 00BC |

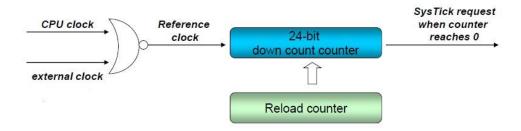

#### 1.5.3 System Timer (SysTick)

The Cortex-M0 includes an integrated system timer, SysTick. SysTick provides a simple, 24-bit clear-on-write, decrementing, wrap-on-zero counter with a flexible control mechanism. The counter can be used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

- SysTick: 24-bit clear-on-write, decrementing, wrap-on-zero counter.

- Is used as a Real Time Operating System (RTOS) tick timer or as a simple counter.

- When enabled, count down from SysTick Current Value Register (SYST\_CVR) to zero, and reload SysTick Reload Value Register (SYST\_RVR), then continue decrement.

- When count down to zero, COUNTFLAG=1. COUNTFLAG=0, on reads.

- SYST\_CVR value is UNKNOWN on reset.

- SYST\_RVR=0, Timer=0. (Disable timer even if Timer is enabled)

Figure 7 Cortex M0 SysTick

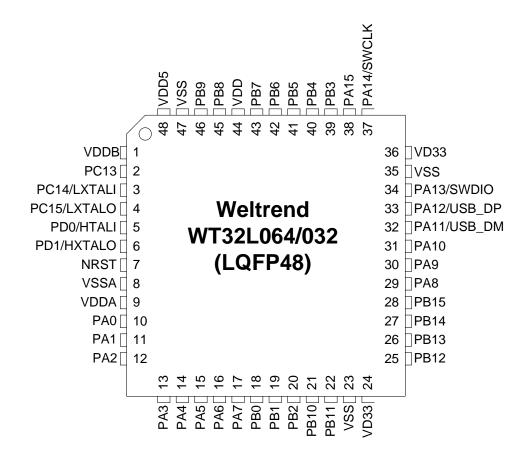

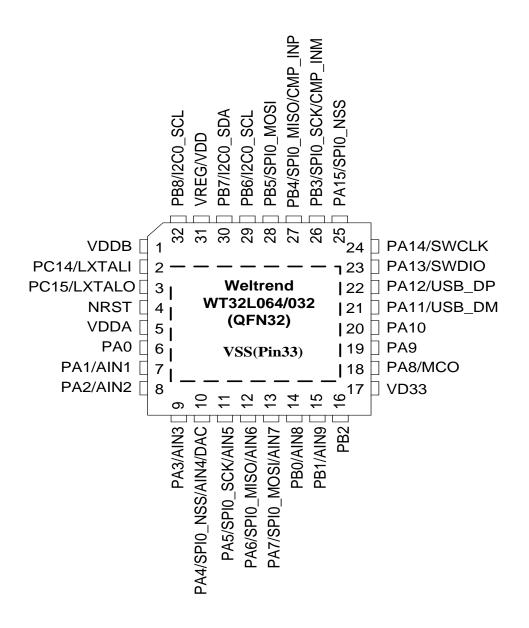

#### 2 Pin Assignment

#### 2.1 Package

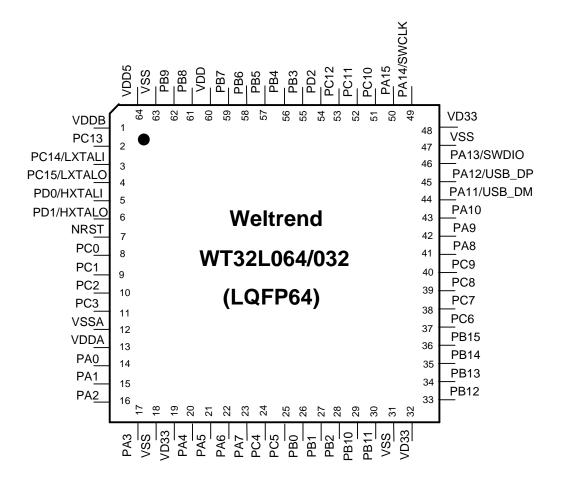

2.1.1 LQFP-64

#### Flash Memory Type 32-bit MCU

#### 2.1.2 LQFP-48

#### 2.1.3 QFN-32

## Flash Memory Type 32-bit MCU

#### 2.2 Pin Description

Table 2 Pin Count Table

| Function LQFP-64 LQFP-48 QFN-32 |                      |                      |                      |  |  |

|---------------------------------|----------------------|----------------------|----------------------|--|--|

|                                 | · ·                  | · ·                  |                      |  |  |

| XTAL                            | 2+2                  | 2+2                  | 1+1                  |  |  |

| ADC                             | 16                   | 10                   | 10                   |  |  |

| DAC                             | 1                    | 1                    | 1                    |  |  |

| comparator                      | 2+2                  | 2+2                  | 2+2                  |  |  |

| USB                             | 1+1                  | 1+1                  | 1+1                  |  |  |

| analog power                    | 1+1                  | 1+1                  | 1+0                  |  |  |

| digital power                   | 3+3                  | 3+3                  | 1+0                  |  |  |

| VBUS power                      | 1+1                  | 1+1                  | 1+1                  |  |  |

| LDO_CORE                        | 1                    | 1                    | 1                    |  |  |

| GPIO                            | 51                   | 37                   | 27                   |  |  |

| serial wire                     | 2                    | 2                    | 2                    |  |  |

| MCO (X1)                        | 1 (with remap)       | 1 (with remap)       | 1 (with remap)       |  |  |

| timer CH (X3)                   | 12 (with remap)      | 12 (with remap)      | 12                   |  |  |

| timer ETR (X1)                  | 1 (with remap)       | 1 (with remap)       | 1 (with remap)       |  |  |

| UART (X2)                       | 2+2 (with remap)     | 2+2 (with remap)     | 2+2 (with remap)     |  |  |

| SPI (X2)                        | 2+2+2+2 (with remap) | 2+2+2+2 (with remap) | 2+2+2+2 (with remap) |  |  |

| I2C (X2)                        | 2+2+2 (with remap)   | 2+2+2 (with remap)   | 1+1+1                |  |  |

| I2S (X1)                        | 1+1+1+1 (with remap) | -                    | -                    |  |  |

| PWM (X4)                        | 4 (with remap)       | 4 (with remap)       | 4 (with remap)       |  |  |

| WKUP                            | 2                    | 2                    | 1                    |  |  |

| PVD_IN                          | 1                    | 1                    | 1                    |  |  |

## Flash Memory Type 32-bit MCU

Table 3 Pin Assignment Table

|            |            |           |      | i abie 3 | Pin Assignm       | T Table                                            |  |

|------------|------------|-----------|------|----------|-------------------|----------------------------------------------------|--|

| LQFP<br>64 | LQFP<br>48 | QFN<br>32 | Name | Туре     | Structure<br>Type | Description                                        |  |

| 1          | 1          | 1         | VDDB | Р        | _                 | battery power pin (RTC)                            |  |

| 2          | 2          |           | PC13 | I/O      | —                 | WKUP1                                              |  |

| 3          | 3          | 2         | PC14 | I/O      | Α                 | LXTALI                                             |  |

| 4          | 4          | 3         | PC15 | I/O      | Α                 | LXTALO                                             |  |

| 5          | 5          |           | PD0  | I/O      | В                 | HXTALI                                             |  |

| 6          | 6          |           | PD1  | I/O      | В                 | HXTALO                                             |  |

| 7          | 7          | 4         | NRST | I        | С                 | active low external reset                          |  |

| 8          |            |           | PC0  | I/O      | A1                | AIN10 / I2S_DIN                                    |  |

| 9          |            |           | PC1  | I/O      | A1                | AIN11 / I2S_DOUT                                   |  |

| 10         |            |           | PC2  | I/O      | A1                | AIN12 / I2S_BCLK                                   |  |

| 11         |            |           | PC3  | I/O      | A1                | AIN13 / I2S_LRCLK / PWM01A                         |  |

| 12         | 8          | 33        | VSSA | Р        | _                 | analog ground pin                                  |  |

| 13         | 9          | 5         | VDDA | Р        | —                 | analog power pin                                   |  |

| 14         | 10         | 6         | PA0  | I/O      | A1                | AIN0 / TMR1_CH0_ETR / WKUP0 /<br>PWM02A/ COMP0_INM |  |

| 15         | 11         | 7         | PA1  | I/O      | A1                | AIN1 / TMR1_CH1 / PWM03A/ COMP0_INP                |  |

| 16         | 12         | 8         | PA2  | I/O      | A1                | AIN2 / UART1_TX / TMR1_CH2                         |  |

|            |            |           |      |          |                   |                                                    |  |

| 17         | 13         | 9         | PA3  | I/O      | A1                | AIN3 / UART1_RX / TMR1_CH3                         |  |

| 18         |            | 33        | VSS  | Р        | —                 | ground pin                                         |  |

| 19         |            |           | VD33 | Р        | _                 | power pin                                          |  |

| 20         | 14         | 10        | PA4  | I/O      | В                 | AIN4 / SPI0_NSS / DAC                              |  |

| 21         | 15         | 11        | PA5  | I/O      | A1                | AIN5 / SPI0_SCK                                    |  |

| 22         | 16         | 12        | PA6  | I/O      | A1                | AIN6 / SPI0_MISO / TMR2_CH0                        |  |

| 23         | 17         | 13        | PA7  | I/O      | A1                | AIN7 / SPI0_MOSI / TMR2_CH1                        |  |

| 24         |            |           | PC4  | I/O      | A1                | AIN14                                              |  |

| 25         |            |           | PC5  | I/O      | A1                | AIN15                                              |  |

| 26         | 18         | 14        | PB0  | I/O      | В                 | AIN8 / TMR2_CH2/EXT_REF                            |  |

| 27         | 19         | 15        | PB1  | I/O      | A1                | AIN9 / TMR2_CH3                                    |  |

| 28         | 20         | 16        | PB2  | I/O      | Α                 | MCO / PWM00A                                       |  |

| 29         | 21         |           | PB10 | I/O      | Α                 | I2C1_SCL / TMR1_CH2                                |  |

| 30         | 22         |           | PB11 | I/O      | Α                 | I2C1_SDA / TMR1_CH3                                |  |

| 31         | 23         | 33        | VSS  | Р        | _                 | ground pin                                         |  |

| 32         | 24         | 17        | VD33 | Р        | —                 | power pin                                          |  |

|            |            |           |      |          |                   |                                                    |  |

| 33         | 25         |           | PB12 | I/O      | Α                 | SPI1_NSS / I2C1_SMBA                               |  |

| 34         | 26         |           | PB13 | I/O      | Α                 | SPI1_SCK                                           |  |

| 35         | 27         |           | PB14 | I/O      | Α                 | SPI1_MISO                                          |  |

| 36         | 28         |           | PB15 | I/O      | Α                 | SPI1_MOSI                                          |  |

## Weltrend 偉詮電子

## WT32L064/032

#### Flash Memory Type 32-bit MCU

| LQFP<br>64 | LQFP<br>48 | QFN<br>32 | Name | Туре | Structure<br>Type     | Description                                               |

|------------|------------|-----------|------|------|-----------------------|-----------------------------------------------------------|

| 37         |            |           | PC6  | I/O  | Α                     | TMR2_CH0 / I2S_DIN                                        |

| 38         |            |           | PC7  | I/O  | A TMR2_CH1 / I2S_DOUT |                                                           |

| 39         |            |           | PC8  | I/O  | Α                     | TMR2_CH2 / I2S_BCLK                                       |

| 40         |            |           | PC9  | I/O  | Α                     | TMR2_CH3 / I2S_LRCLK                                      |

| 41         | 29         | 18        | PA8  | I/O  | Α                     | MCO / TMR0_CH0 / PWM01B                                   |

| 42         | 30         | 19        | PA9  | I/O  | Α                     | UART0_TX / TMR0_CH1 / PWM02B                              |

| 43         | 31         | 20        | PA10 | I/O  | Α                     | UART0_RX / TMR0_CH2 / PWM03B                              |

| 44         | 32         | 21        | PA11 | I/O  | В                     | USB_DM / TMR0_CH3                                         |

| 45         | 33         | 22        | PA12 | I/O  | В                     | USB_DP                                                    |

| 46         | 34         | 23        | PA13 | I/O  | Α                     | SWDIO                                                     |

| 47         | 35         | 33        | VSS  | Р    | _                     | ground pin                                                |

| 48         | 36         |           | VD33 | Р    | _                     | power pin                                                 |

|            |            |           |      |      |                       |                                                           |

| 49         | 37         | 24        | PA14 | I/O  | Α                     | SWCLK                                                     |

| 50         | 38         | 25        | PA15 | I/O  | Α                     | TMR1_CH0_ETR / SPI0_NSS                                   |

| 51         |            |           | PC10 | I/O  | Α                     | TMR0_CH0 / I2C1_SCL                                       |

| 52         |            |           | PC11 | I/O  | Α                     | TMR0_CH1 / I2C1_SDA                                       |

| 53         |            |           | PC12 | I/O  | Α                     | TMR0_CH2                                                  |

| 54         |            |           | PD2  | I/O  | Α                     | TMR0_CH3                                                  |

| 55         | 39         | 26        | PB3  | I/O  | <b>A1</b>             | TMR1_CH1 / SPI0_SCK / COMP1_INM                           |

| 56         | 40         | 27        | PB4  | I/O  | A1                    | SPI0_MISO / COMP1_INP                                     |

| 57         | 41         | 28        | PB5  | I/O  | Α                     | I2C0_SMBA / SPI0_MOSI                                     |

| 58         | 42         | 29        | PB6  | I/O  | Α                     | I2C0_SCL / UART0_TX / PWM00B                              |

| 59         | 43         | 30        | PB7  | I/O  | A1                    | I2C0_SDA / UART0_RX / PVD_IN                              |

| 60         | 44         | 31        | VDD  | Р    | _                     | regulator core power output, connect to bypass capacitor. |

| 61         | 45         | 32        | PB8  | I/O  | Α                     | I2C0_SCL / UART1_TX                                       |

| 62         | 46         |           | PB9  | I/O  | Α                     | I2C0_SDA / UART1_RX                                       |

| 63         | 47         | 33        | VSS  | Р    | —                     | ground pin                                                |

| 64         | 48         |           | VDD5 | Р    | _                     | VBUS power pin                                            |

**GPIO Structure Type:**

A: 5V Tolerant I/O

B: STD 3.3V I/O

C: Bidirection reset with embedded weak pull-up resistor

A1: 5V Tolerant I/O: Only at Digital Mode but exclude Analog Mode.

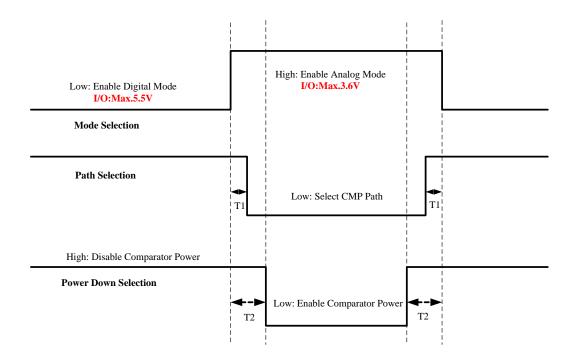

- ✓ Most **A1** type default is analog mode (3.3V) during **RESET period**, must avoid to connect 5V application and please choose **A** type I/O if necessary.

- ✓ If used in A1 Type, the timing procedure must follow below comparator example.

(Avoid hardware damage in 3.3V Analog mode caused by 5V input in Digital mode)

## Flash Memory Type 32-bit MCU

#### 2.3 Alternate Function I/O Priority

| Name        | AF_SEL 0 | AF_SEL 1             | AF_SEL 2                 | AF_SEL 3     | AF_SEL 4       | AF_SEL 5    | Analog                    |

|-------------|----------|----------------------|--------------------------|--------------|----------------|-------------|---------------------------|

| PA0         |          |                      |                          |              | TMR1_CH0_ETR   | PWM02A      | WKUP0 / AIN0/<br>COM0_INM |

| PA1         |          |                      |                          |              | TMR1_CH1       | PWM03A      | AIN1/COM0_INP             |

| PA2         |          |                      | UART1_TX                 |              | TMR1_CH2       |             | AIN2                      |

| PA3         |          |                      | UART1_RX                 |              | TMR1_CH3       |             | AIN3                      |

| PA4         |          |                      |                          | SPI0_NSS     |                |             | AIN4 / DAC                |

| PA5         |          |                      |                          | SPI0_SCK     |                |             | AIN5                      |

| PA6         |          |                      |                          | SPI0_MISO    | TMR2_CH0       |             | AIN6                      |

| PA7         |          |                      |                          | SPI0_MOSI    | TMR2_CH1       |             | AIN7                      |

| PA8         |          | MCO                  |                          |              | TMR0_CH0       | PWM01B      |                           |

| PA9         |          |                      | UART0_TX                 |              | TMR0_CH1       | PWM02B      |                           |

| PA10        |          |                      | UART0_RX                 |              | TMR0_CH2       | PWM03B      |                           |

| PA11        |          |                      | _                        |              | TMR0_CH3       |             | USB_DM                    |

| PA12        |          |                      |                          |              |                |             | USB_DP                    |

| PA13        | SWDIO    |                      |                          |              |                |             | _                         |

| PA14        | SWCLK    |                      |                          |              |                |             |                           |

| PA15        | 00=      |                      |                          | (SPI0_NSS)   | (TMR1_CH0_ETR) |             |                           |

| PB0         |          |                      |                          | (61 10_1166) | TMR2_CH2       |             | AIN8/EXT_REF              |

| PB1         |          |                      |                          |              | TMR2_CH3       |             | AIN9                      |

| PB2         |          | MCO                  |                          |              | TWINZ_OTTO     | PWM00A      | All Vo                    |

| PB3         |          | IVICO                |                          | (SPI0_SCK)   | (TMR1_CH1)     | I WIVIOUA   | COMP1_INM                 |

| PB4         |          |                      |                          | (SPI0_MISO)  | (TWINT_CITT)   |             | COMP1_INP                 |

| PB5         |          | I2C0_SMBA            |                          | (SPI0_MOSI)  |                |             | COIVII I_IIVI             |

| PB6         |          | I2C0_SIVIDA          | (UART0_TX)               | (3F10_10031) |                | PWM00B      |                           |

| PB7         |          | I2C0_SCL<br>I2C0_SDA | (UARTO_TX)               |              |                | PVVIVIOUD   | PVD IN                    |

| PB8         |          | (I2C0_SDA            | (UARTO_RX)<br>(UART1_TX) |              |                | +           | FVD_IN                    |

|             |          |                      |                          |              |                |             |                           |

| PB9<br>PB10 |          | (I2C0_SDA)           | (UART1_RX)               |              | (TMD4 CH2)     |             |                           |

|             |          | I2C1_SCL             |                          |              | (TMR1_CH2)     |             |                           |

| PB11        |          | I2C1_SDA             |                          | ODIA NOO     | (TMR1_CH3)     |             |                           |

| PB12        |          | I2C1_SMBA            |                          | SPI1_NSS     |                |             |                           |

| PB13        |          |                      |                          | SPI1_SCK     |                |             |                           |

| PB14        |          |                      |                          | SPI1_MISO    |                |             |                           |

| PB15        |          | IOO DINI             |                          | SPI1_MOSI    |                |             | AINIAO                    |

| PC0         |          | I2S_DIN              |                          |              |                |             | AIN10                     |

| PC1         |          | I2S_DOUT             |                          |              |                |             | AIN11                     |

| PC2         |          | I2S_BCLK             |                          |              |                | DVA/A40.4.A | AIN12                     |

| PC3         |          | I2S_LRCLK            |                          |              |                | PWM01A      | AIN13                     |

| PC4         |          |                      |                          |              |                |             | AIN14                     |

| PC5         |          | (100 DIV)            |                          |              | (TMD0, OUG)    |             | AIN15                     |

| PC6         |          | (I2S_DIN)            |                          |              | (TMR2_CH0)     |             |                           |

| PC7         |          | (I2S_DOUT)           |                          |              | (TMR2_CH1)     |             |                           |

| PC8         |          | (I2S_BCLK)           |                          |              | (TMR2_CH2)     |             |                           |

| PC9         |          | (I2S_LRCLK)          |                          |              | (TMR2_CH3)     |             |                           |

| PC10        |          | (I2C1_SCL)           |                          |              | (TMR0_CH0)     |             |                           |

| PC11        |          | (I2C1_SDA)           |                          |              | (TMR0_CH1)     |             |                           |

| PC12        |          |                      |                          |              | (TMR0_CH2)     |             | 11000                     |

| PC13        |          |                      |                          |              |                |             | WKUP1                     |

| PC14        |          |                      |                          |              |                | 1           | LXTALI                    |

| PC15        |          |                      |                          |              |                |             | LXTALO                    |

| PD0         |          |                      |                          |              |                |             | HXTALI                    |

| PD1         |          |                      |                          |              |                |             | HXTALO                    |

| PD2         |          |                      |                          |              | (TMR0_CH3)     |             |                           |

Note: () means lower priority for port inputs

#### 3 Memory Mapping

#### 3.1 AMBA Bus Address Mapping

| Index                    | Function          | Description |

|--------------------------|-------------------|-------------|

| 0x0000_0000~0x1FEF_FFFF  | reserved          |             |

| 0x1000_0000~0x1000_FFFF  | embedded flash    | 64KB        |

| 0x1FF0_0000~0x1FF0_07FF  | reserved          |             |

| 0x1FF0_0800~0x1FF0_FFFF  | reserved          |             |

| 0x1FF1_0000~0x1FF1_1FFF  | boot ROM          | 8KB         |

| 0x1FF1_2000~0x1FFF_FFFF  | reserved          |             |

| 0x2000_0000~0x2000_1FFF  | SRAM              | 8KB         |

| 0x2000_5000~0x2FFF_FFFF  | reserved          |             |

| 0x3000_0000~0x3000_0FFF  | DMA buffer        | 4KB         |

| 0x3000_1000~0x3FFF_FFFF  | reserved          |             |

| 0x4000_0000~0x4003_FFFF  | APB0 memory space | 256KB       |

| 0x4004_0000~0x4007_FFFF  | APB1 memory space | 256KB       |

| 0x4008_0000~0x400B_FFFF  | AHB memory space  | 256KB       |

| 0x400C_0000~0xDFFF_FFFF  | reserved          |             |

| 0xE000_0000~0xE00F_FFFF  | reserved          |             |

| 0xE010_0000~0xFFFF_FFF   | reserved          |             |

| 0xF000_0000~0xF000_003FF | System ROM Table  |             |

| 0xF000_0400~0xFFFF_FFF   | reserved          |             |

#### 3.2 APB Memory Space

| Range | Index                   | Function | Description |

|-------|-------------------------|----------|-------------|

| APB0  | 0x4000_0000~0x4000_0FFF |          |             |

|       | 0x4000_1000~0x4000_1FFF |          |             |

|       | 0x4000_2000~0x4000_2FFF | -        |             |

|       | 0x4000_3000~0x4000_3FFF | -        |             |

|       | 0x4000_4000~0x4000_4FFF | UART1    |             |

|       | 0x4000_5000~0x4000_5FFF | -        |             |

|       | 0x4000_6000~0x4000_6FFF | SPI1     |             |

|       | 0x4000_7000~0x4000_7FFF | -        |             |

|       | 0x4000_8000~0x4000_8FFF | I2C0     |             |

|       | 0x4000_9000~0x4000_9FFF | I2C1     |             |

|       | 0x4000_A000~0x4000_AFFF | -        |             |

|       | 0x4000_B000~0x4000_BFFF | -        |             |

|       | 0x4000_C000~0x4000_CFFF |          |             |

|       | 0x4000_D000~0x4000_DFFF | -        |             |

|       | 0x4000_E000~0x4000_EFFF | USB      |             |

|       | 0x4000_F000~0x4000_FFFF | -        |             |

|       | 0x4001_0000~0x4001_0FFF | DAC      |             |

|       | 0x4001_1000~0x4001_1FFF | -        |             |

|       | 0x4001_2000~0x4001_2FFF |          |             |

|       | 0x4001_3000~0x4001_3FFF | -        |             |

## Flash Memory Type 32-bit MCU

| Range | Index                   | Function | Description           |

|-------|-------------------------|----------|-----------------------|

|       | 0x4001 4000~0x4001 4FFF | TMR2     | P. C                  |

|       | 0x4001 5000~0x4001 5FFF | -        |                       |

|       | 0x4001 6000~0x4001 6FFF | -        |                       |

|       | 0x4001 7000~0x4001 7FFF | =        |                       |

|       | 0x4001 8000~0x4001 8FFF | IWDT     |                       |

|       | 0x4001_9000~0x4001_9FFF | WWDT     |                       |

|       | 0x4001 A000~0x4001 AFFF | PMU      | power management unit |

|       | 0x4001_B000~0x4001_BFFF | RTC      |                       |

|       | 0x4001 C000~0x4001 CFFF | PWM      |                       |

|       | 0x4001 D000~0x4001 DFFF | -        |                       |

|       | 0x4001_E000~0x4001_EFFF | -        |                       |

|       | 0x4001_F000~0x4001_FFFF | -        |                       |

| APB1  | 0x4004_0000~0x4004_0FFF | -        |                       |

|       | 0x4004_1000~0x4004_1FFF | -        |                       |

|       | 0x4004_2000~0x4004_2FFF | -        |                       |

|       | 0x4004_3000~0x4004_3FFF | -        |                       |

|       | 0x4004_4000~0x4004_4FFF | UART0    |                       |

|       |                         |          |                       |

|       | 0x4004_6000~0x4004_6FFF | SPI0     |                       |

|       | 0x4004_7000~0x4004_7FFF | -        |                       |

|       | 0x4004_8000~0x4004_8FFF | -        |                       |

|       | 0x4004_9000~0x4004_9FFF | -        |                       |

|       | 0x4004_A000~0x4004_AFFF | -        |                       |

|       | 0x4004_B000~0x4004_BFFF | -        |                       |

|       | 0x4004_C000~0x4004_CFFF | I2S      |                       |

|       | 0x4004_D000~0x4004_DFFF | -        |                       |

|       | 0x4004_E000~0x4004_EFFF | -        |                       |

|       | 0x4004_F000~0x4004_FFFF | -        |                       |

|       | 0x4005_0000~0x4005_0FFF | ADC      |                       |

|       | 0x4005_1000~0x4005_1FFF | -        |                       |

|       | 0x4005_2000~0x4005_2FFF | -        |                       |

|       | 0x4005_3000~0x4005_3FFF | -        |                       |

|       | 0x4005_4000~0x4005_4FFF | TMR0     |                       |

|       | 0x4005_5000~0x4005_5FFF | TMR1     |                       |

|       | 0x4005_6000~0x4005_6FFF | -        |                       |

|       | 0x4005_7000~0x4005_7FFF | -        |                       |

|       |                         |          |                       |

|       | 0x4005_9000~0x4005_9FFF | CRS      |                       |

|       | 0x4005_A000~0x4005_AFFF | -        |                       |

|       | 0x4005_B000~0x4005_BFFF | -        |                       |

|       | 0x4005_C000~0x4005_CFFF | -        |                       |

|       | 0x4005_D000~0x4005_DFFF | -        |                       |

|       | 0x4005_E000~0x4005_EFFF | -        |                       |

|       | 0x4005_F000~0x4005_FFFF | -        |                       |

| AHB   | 0x4008_0000~0x4008_0FFF | FLASH    | flash control         |

|       | 0x4008_1000~0x4008_1FFF | -        |                       |

|       | 0x4008_2000~0x4008_2FFF | DMA      |                       |

|       | 0x4008_3000~0x4008_3FFF | -        |                       |

## Flash Memory Type 32-bit MCU

| Range | Index                   | Function       | Description |

|-------|-------------------------|----------------|-------------|

|       | 0x4008_4000~0x4008_4FFF | RCC            |             |

|       | 0x4008_5000~0x4008_5FFF | -              |             |

|       | 0x4008_6000~0x4008_6FFF | -              |             |

|       | 0x4008_7000~0x4008_7FFF | -              |             |

|       |                         |                |             |

|       | 0x4008_9000~0x4008_9FFF | -              |             |

|       | 0x4008_A000~0x4008_AFFF | CRC32          |             |

|       | 0x4008_B000~0x4008_BFFF | -              |             |

|       | 0x4008_C000~0x4008_CFFF | GPIO           |             |

|       | 0x4008_D000~0x4008_DFFF | -              |             |

|       | 0x4008_E000~0x4008_EFFF | -              |             |

|       | 0x4008_F000~0x4008_FFFF | -              |             |

|       | 0x5001_F000~0x5001_FFFF | system control |             |

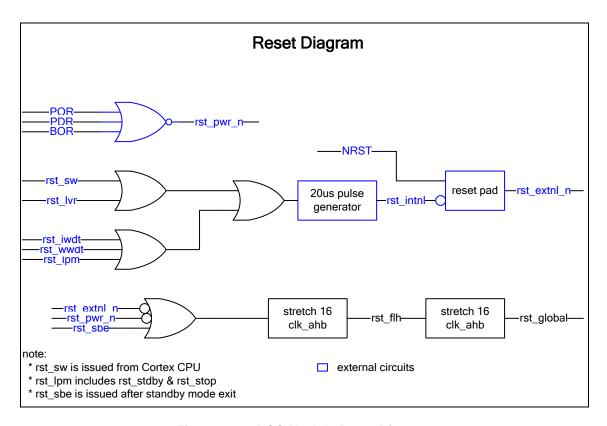

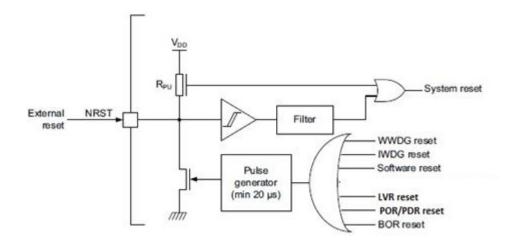

#### 4 Reset and Clock Control

#### 4.1 Main Features

The Reset and Clock Control (RCC) is used to control miscellaneous resets and clocks of system.

- Reset outputs: